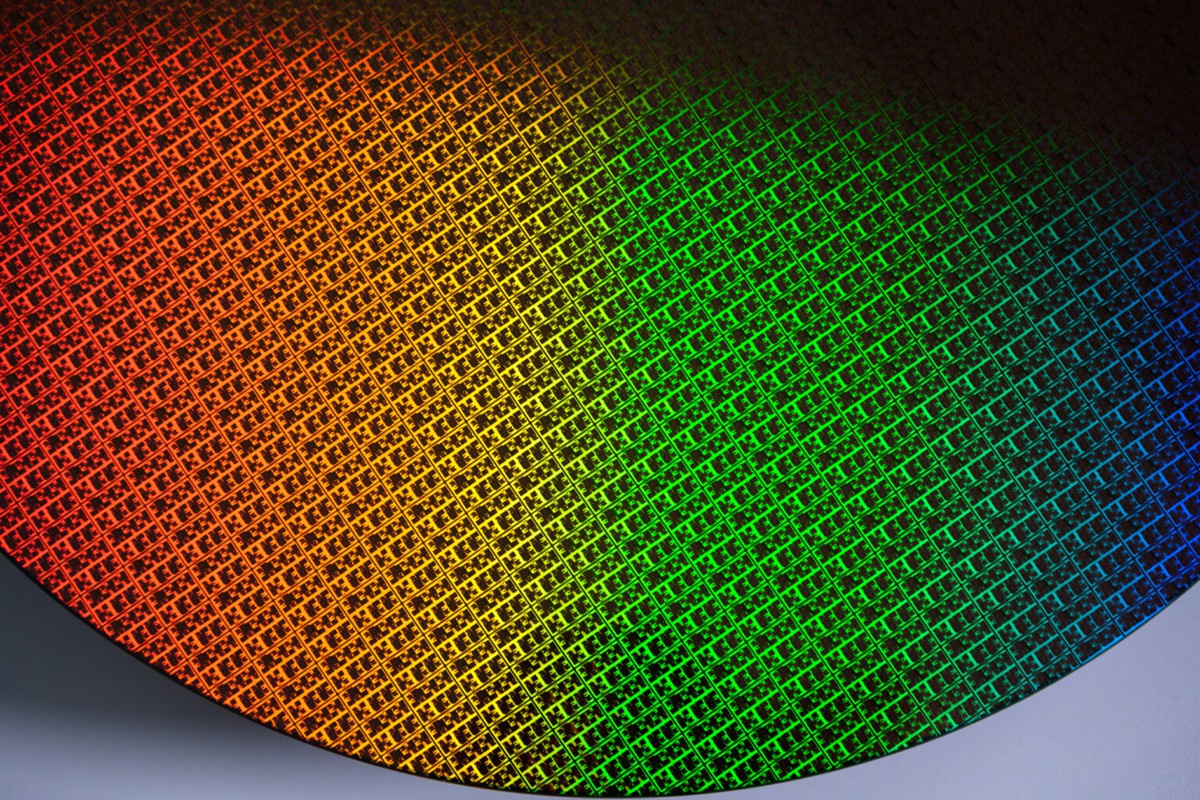

Intel 近日在 Tech Tour 技術活動上公佈最新進展,指出旗下備受矚目的 18A 製程 已達到「歷史新低的缺陷密度」,顯示良率表現穩定,預計將於今年第 4 季進入量產階段,為自家與外部代工客戶做好準備。

這次的 18A 節點對 Intel 意義重大,不只是公司自成立晶圓代工業務以來的關鍵里程碑,也受到政界與產業界的高度關注。Intel 表示,目前 18A 的製程缺陷密度創下新低,這代表晶圓上的瑕疵數量更少、晶片功能失效的機率更低,整體良率可望達到量產水準。

簡單來說,「缺陷密度(Defect Density)」指的是晶圓單位面積中存在的瑕疵數量。如果密度太高,像是晶片面積較大的設計就更容易受到影響,導致部分電晶體或導線無法正常工作。而這次 18A 能將缺陷密度壓到歷史低點,意味著 Intel 的製程控制已相當成熟,足以支撐大型晶片設計與高效能運算(HPC)等市場需求。

過去曾有傳聞稱 Intel 18A 的良率一度僅約 10%,但從目前的情況來看,這數字顯然已經大幅改善。Intel 決定在今年加速 18A 的量產準備,也間接證明製程穩定性已達標。雖然「缺陷密度」並非評估良率的唯一因素,仍需搭配其他指標(例如參數失效、光罩誤差與製程餘裕)綜合分析,不過這項指標已足以說明 Intel 在製程研發上的突破。

隨著 18A 製程良率提升,Intel 預計將與台積電 N2、三星 SF2 展開直接競爭。若進展持續順利,18A 也可能成為美國半導體產業重新突圍的重要基石。

來源

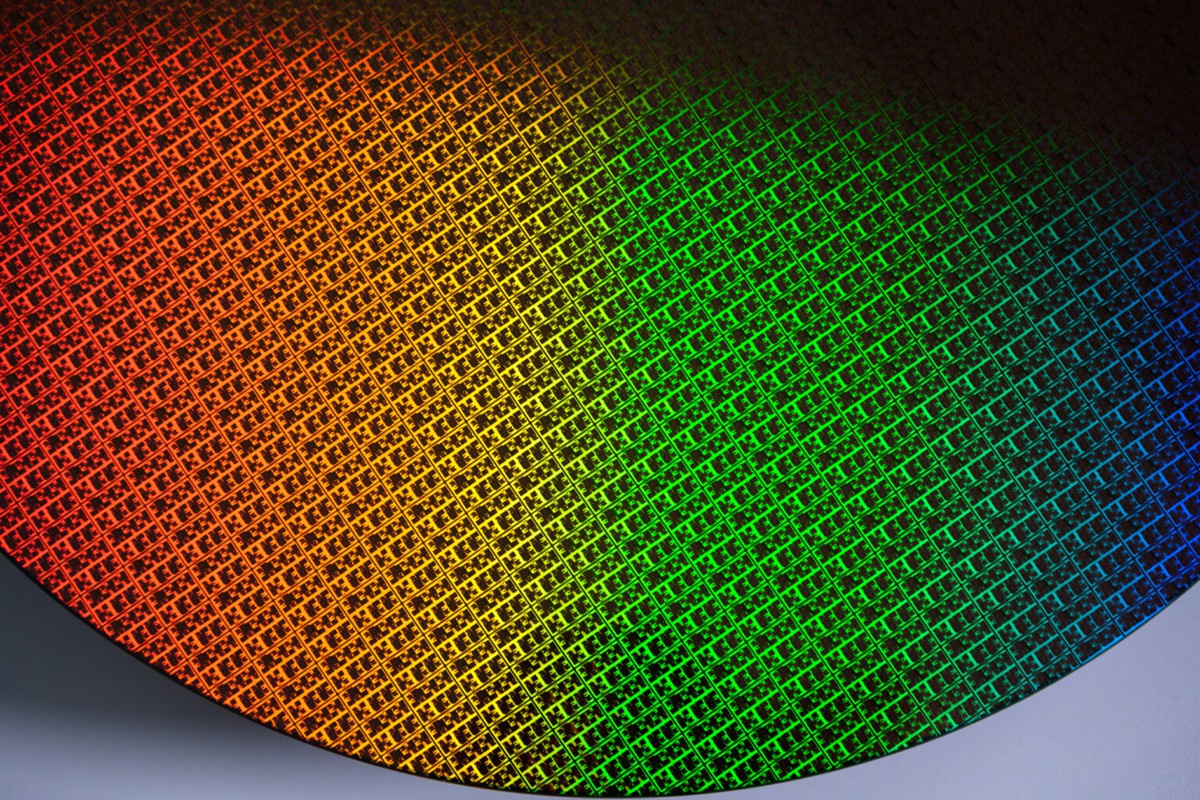

這次的 18A 節點對 Intel 意義重大,不只是公司自成立晶圓代工業務以來的關鍵里程碑,也受到政界與產業界的高度關注。Intel 表示,目前 18A 的製程缺陷密度創下新低,這代表晶圓上的瑕疵數量更少、晶片功能失效的機率更低,整體良率可望達到量產水準。

簡單來說,「缺陷密度(Defect Density)」指的是晶圓單位面積中存在的瑕疵數量。如果密度太高,像是晶片面積較大的設計就更容易受到影響,導致部分電晶體或導線無法正常工作。而這次 18A 能將缺陷密度壓到歷史低點,意味著 Intel 的製程控制已相當成熟,足以支撐大型晶片設計與高效能運算(HPC)等市場需求。

過去曾有傳聞稱 Intel 18A 的良率一度僅約 10%,但從目前的情況來看,這數字顯然已經大幅改善。Intel 決定在今年加速 18A 的量產準備,也間接證明製程穩定性已達標。雖然「缺陷密度」並非評估良率的唯一因素,仍需搭配其他指標(例如參數失效、光罩誤差與製程餘裕)綜合分析,不過這項指標已足以說明 Intel 在製程研發上的突破。

隨著 18A 製程良率提升,Intel 預計將與台積電 N2、三星 SF2 展開直接競爭。若進展持續順利,18A 也可能成為美國半導體產業重新突圍的重要基石。

來源