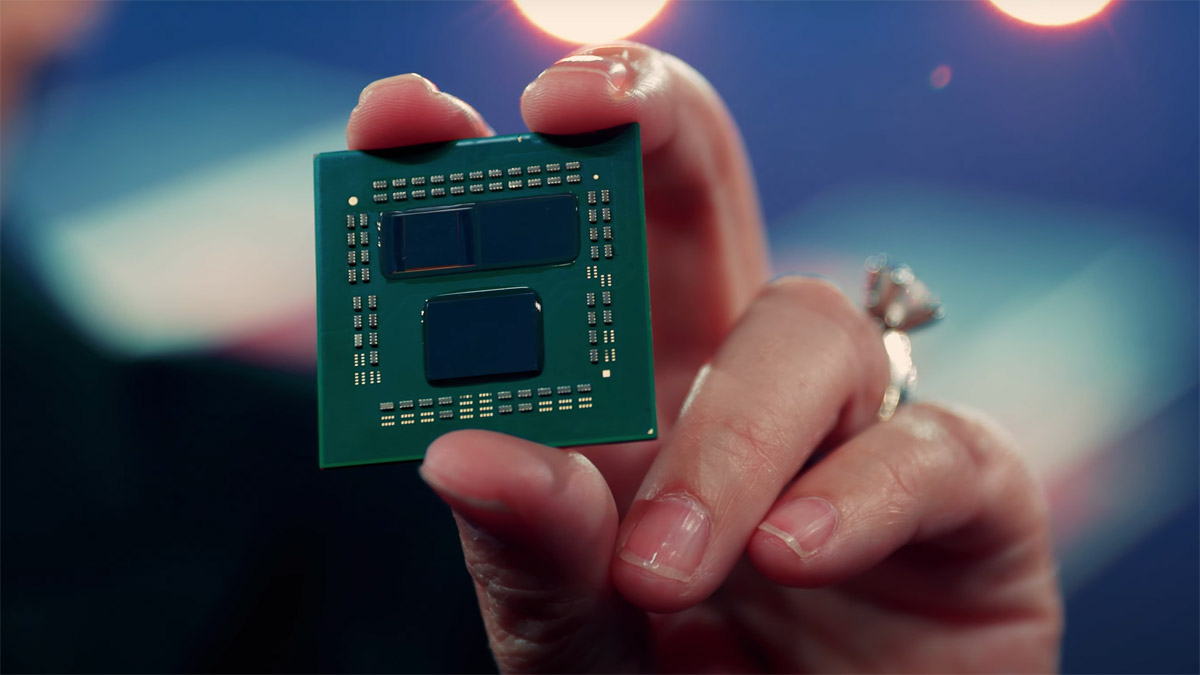

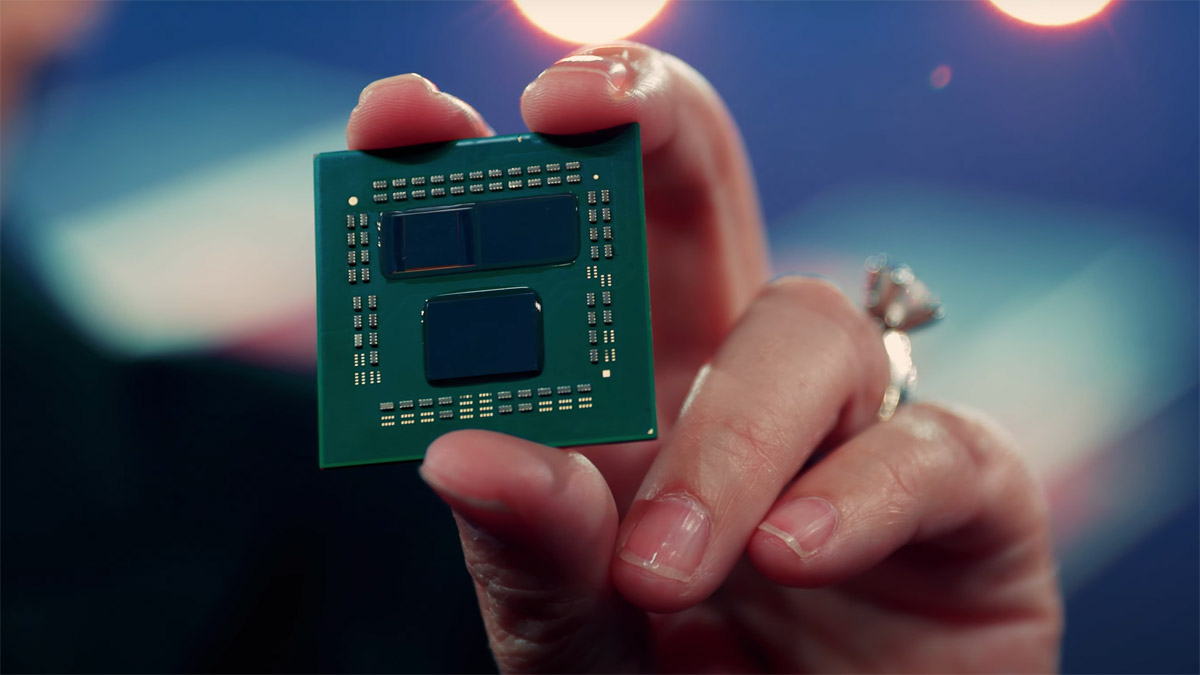

AMD 預計將在 CES 2026 發表新一代 Ryzen 9000X3D 處理器,而後續的 Zen 6 架構同樣會延續 3D V-Cache 設計。由於 Zen 6 每個 CCD 的核心數將從現行的 8 核提升至 12 核,L3 快取容量也勢必同步增加。

根據來源消息,Zen 6 X3D 處理器在單 CCD 配置下,L3 快取總容量可達 144MB;若是雙 CCD 設計,則直接翻倍來到 288MB。這裡指的都是搭載 3D V-Cache 的版本。從核心數成長比例推算,標準的 Zen 6 CCD 本身應會配置 48MB L3 快取,再疊加 96MB 的 3D V-Cache,合計就是 144MB;雙 CCD 則是翻倍。

這樣的快取規模,也與 Intel 傳聞中的 Nova Lake 架構相當接近。先前就有消息指出,Nova Lake 將推出搭載 bLLC(big Last Level Cache)的版本,單一運算模組可達 144MB,雙模組則為 288MB。不過,Intel 將如何在消費級平台上實現 bLLC,目前仍不明朗。現行的 Clearwater Forest Xeon 是將 L3 快取與記憶體控制器放在基礎模組上,但 Nova Lake 似乎不會沿用相同的封裝方式。

在製程方面,Zen 6 的 CCD 預計採用台積電 N2P 製程,而 IOD 則為 N3P 製程。此外,CCD 與 IOD 之間的互連架構也將迎來重大變革,預計不再使用自 Zen 2 時代沿用至今的 SerDes 方案,而是改採類似 Strix Halo 所使用的高頻寬平行介面,在頻寬、延遲與能效表現上都有明顯提升。

根據來源消息,Zen 6 X3D 處理器在單 CCD 配置下,L3 快取總容量可達 144MB;若是雙 CCD 設計,則直接翻倍來到 288MB。這裡指的都是搭載 3D V-Cache 的版本。從核心數成長比例推算,標準的 Zen 6 CCD 本身應會配置 48MB L3 快取,再疊加 96MB 的 3D V-Cache,合計就是 144MB;雙 CCD 則是翻倍。

這樣的快取規模,也與 Intel 傳聞中的 Nova Lake 架構相當接近。先前就有消息指出,Nova Lake 將推出搭載 bLLC(big Last Level Cache)的版本,單一運算模組可達 144MB,雙模組則為 288MB。不過,Intel 將如何在消費級平台上實現 bLLC,目前仍不明朗。現行的 Clearwater Forest Xeon 是將 L3 快取與記憶體控制器放在基礎模組上,但 Nova Lake 似乎不會沿用相同的封裝方式。

在製程方面,Zen 6 的 CCD 預計採用台積電 N2P 製程,而 IOD 則為 N3P 製程。此外,CCD 與 IOD 之間的互連架構也將迎來重大變革,預計不再使用自 Zen 2 時代沿用至今的 SerDes 方案,而是改採類似 Strix Halo 所使用的高頻寬平行介面,在頻寬、延遲與能效表現上都有明顯提升。