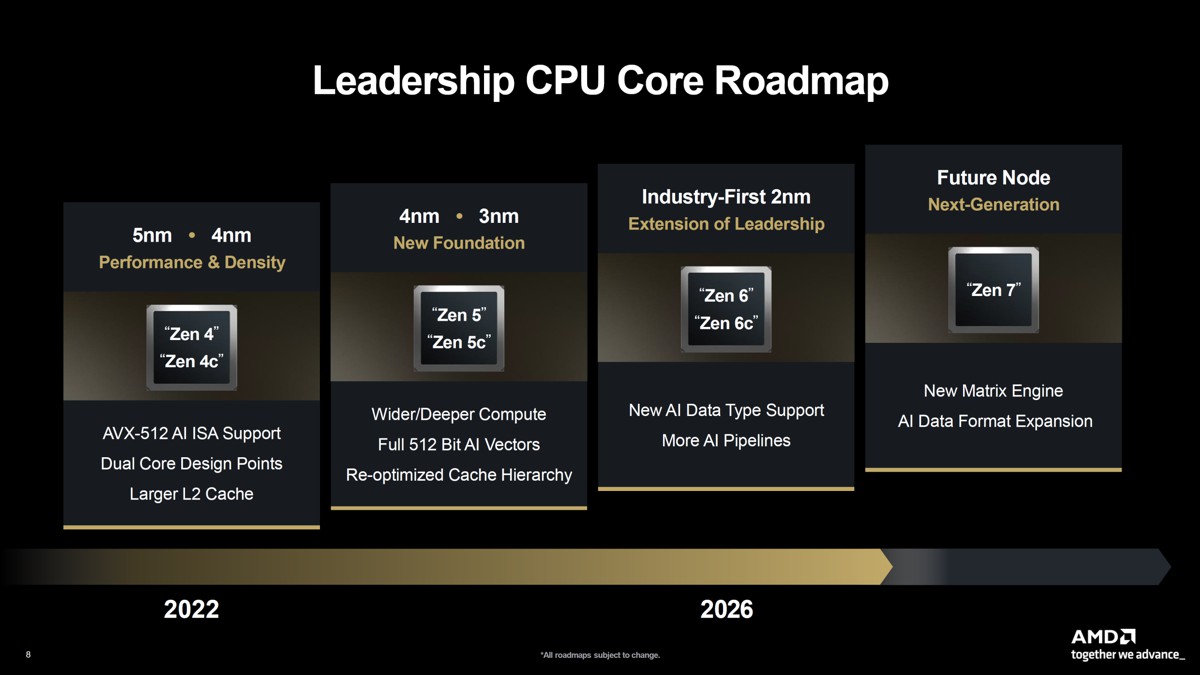

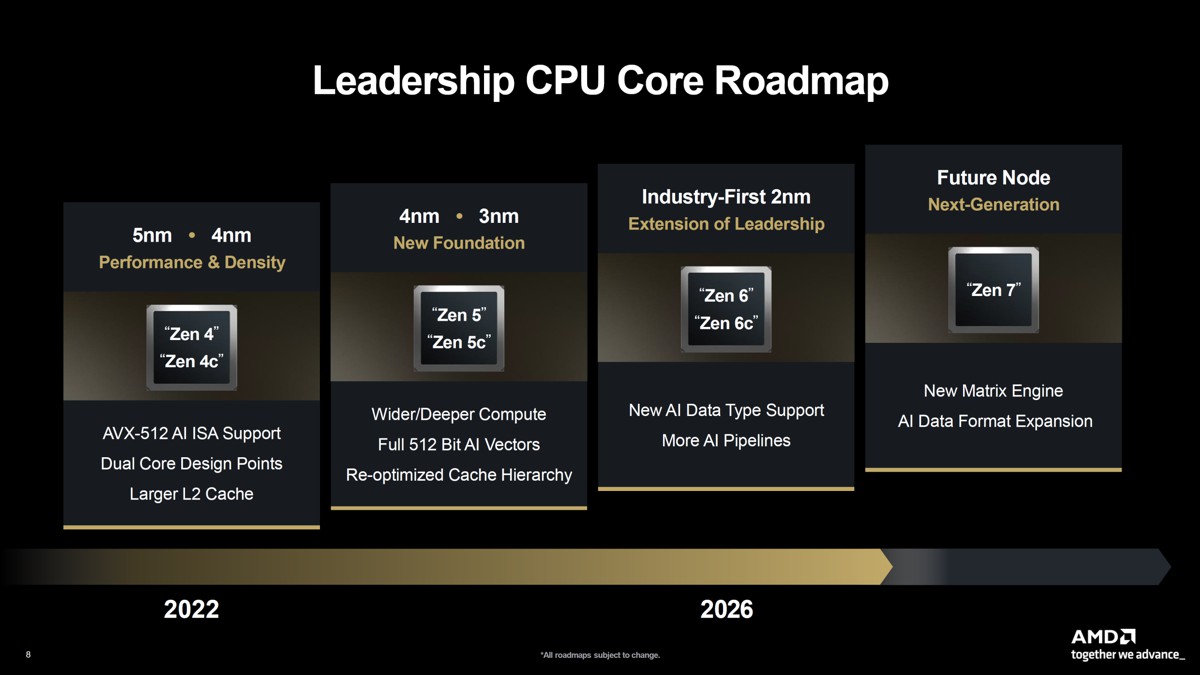

AMD 下一代 Zen 6 架構處理器預計將於今年登場,隨著資訊逐步曝光,最新傳聞也揭露了 Zen 6 的 CCD(Core Complex Die)細節,顯示在製程與密度方面將有明顯突破。

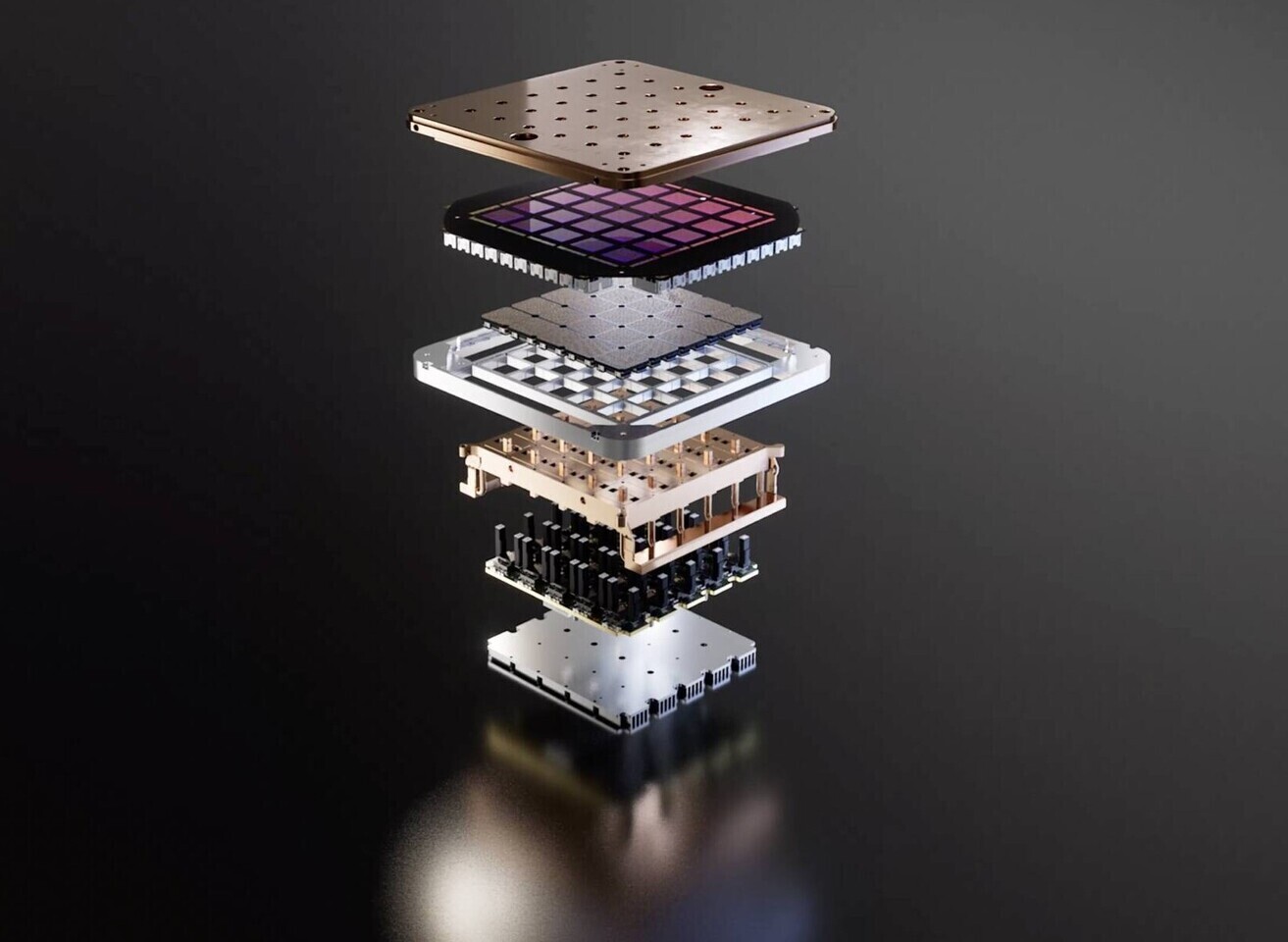

消息來源指出,Zen 6 CCD 將採用 台積電 N2(2nm)製程打造。爆料者 HXL(@9550pro)整理了自 Zen 2 以來各世代 CCD 的晶片面積數據,而 Zen 6 CCD 的面積據稱約為 76mm²,與 Zen 5(約 71mm²)與 Zen 4(約 72mm²)相當接近,僅增加約 5~7%,但核心與快取規模卻大幅提升。

根據資料對比:

Zen 6 CCD 每顆將配置 12 核心(上一代為 8 核)與 48MB L3 快取(上一代 32MB),等於在面積變化不大的情況下,核心與快取容量直接增加 50%,顯示 N2 製程在電晶體密度上的優勢相當明顯。

AMD 先前已確認,搭載 Zen 6 CCD 的 EPYC Venice 將是首批採用台積電 N2 NanoSheet 製程的產品。後續亦有說法指出,完整 Zen 6 家族可能改用改良版 N2P 製程,而 I/O Die 則採用 N3P,部分入門產品仍可能沿用 N3P。

目前對於 Zen 6 桌面處理器的推測包括:

另外還有關於 Zen 6C(高密度核心版本)的說法,指出單顆 CCD 面積約 156mm²,卻可整合 32 核心與 128MB L3 快取。相較標準 Zen 6 CCD,面積約增加 2 倍,但核心數翻倍、快取容量提升至 2.66 倍,顯示 AMD 在資料中心市場仍會持續推進高核心密度設計。

Zen 6 的重點不只在 IPC 與時脈優化,更在於透過新製程帶來的核心與快取規模擴張。未來搭載新一代 X3D 3D V-Cache 的版本,也可能迎來第三代技術升級。首波 Zen 6 產品預計下半年推出,涵蓋 EPYC Venice 與新一代 Ryzen 平台。

來源

消息來源指出,Zen 6 CCD 將採用 台積電 N2(2nm)製程打造。爆料者 HXL(@9550pro)整理了自 Zen 2 以來各世代 CCD 的晶片面積數據,而 Zen 6 CCD 的面積據稱約為 76mm²,與 Zen 5(約 71mm²)與 Zen 4(約 72mm²)相當接近,僅增加約 5~7%,但核心與快取規模卻大幅提升。

根據資料對比:

| 架構 | 核心數 | L3 快取 | 製程 | CCD 面積 |

|---|---|---|---|---|

| Zen 4 | 8 核 | 32MB | TSMC N5 | ~72mm² |

| Zen 5 | 8 核 | 32MB | TSMC N4 | ~71mm² |

| Zen 6 | 12 核 | 48MB | TSMC N2 | ~76mm² |

Zen 6 CCD 每顆將配置 12 核心(上一代為 8 核)與 48MB L3 快取(上一代 32MB),等於在面積變化不大的情況下,核心與快取容量直接增加 50%,顯示 N2 製程在電晶體密度上的優勢相當明顯。

AMD 先前已確認,搭載 Zen 6 CCD 的 EPYC Venice 將是首批採用台積電 N2 NanoSheet 製程的產品。後續亦有說法指出,完整 Zen 6 家族可能改用改良版 N2P 製程,而 I/O Die 則採用 N3P,部分入門產品仍可能沿用 N3P。

目前對於 Zen 6 桌面處理器的推測包括:

- 兩位數幅度 IPC 提升

- 核心與執行緒數量進一步增加(可能達 24 核 48 線程)

- 更高時脈表現

- 每顆 CCD 最高 48MB L3 快取

- 最多 2 顆 CCD 搭配 1 顆 IOD

- 支援更高頻率 DDR5 記憶體

- 雙記憶體控制器設計(但維持雙通道)

- TDP 等級與現行世代接近

另外還有關於 Zen 6C(高密度核心版本)的說法,指出單顆 CCD 面積約 156mm²,卻可整合 32 核心與 128MB L3 快取。相較標準 Zen 6 CCD,面積約增加 2 倍,但核心數翻倍、快取容量提升至 2.66 倍,顯示 AMD 在資料中心市場仍會持續推進高核心密度設計。

Zen 6 的重點不只在 IPC 與時脈優化,更在於透過新製程帶來的核心與快取規模擴張。未來搭載新一代 X3D 3D V-Cache 的版本,也可能迎來第三代技術升級。首波 Zen 6 產品預計下半年推出,涵蓋 EPYC Venice 與新一代 Ryzen 平台。

來源