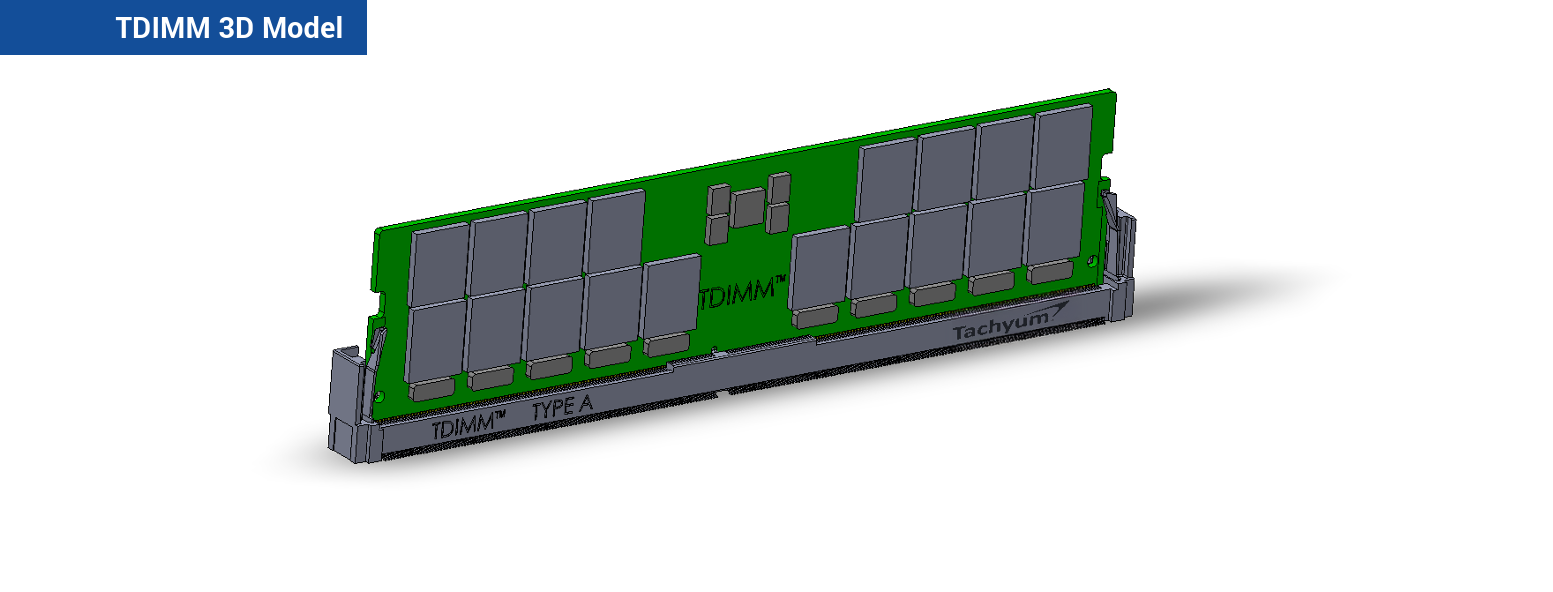

Tachyum 近日公布自家全新的開放式記憶體標準 TDIMM(Tachyum DIMM),主打顯著的頻寬提升與更高模組容量,目標瞄準 AI 與大型資料中心環境。

TDIMM 的容量也隨不同外形尺寸而異:

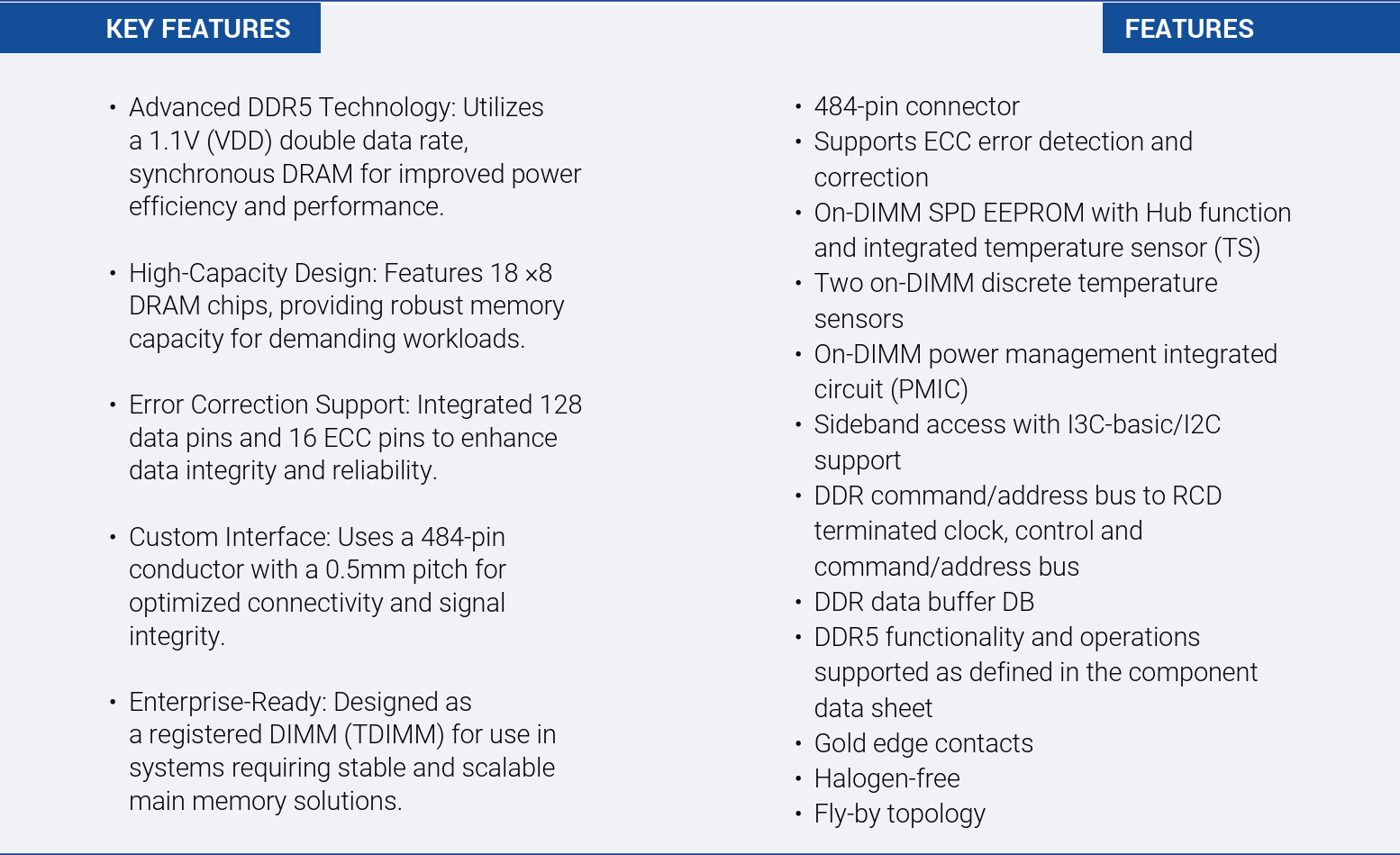

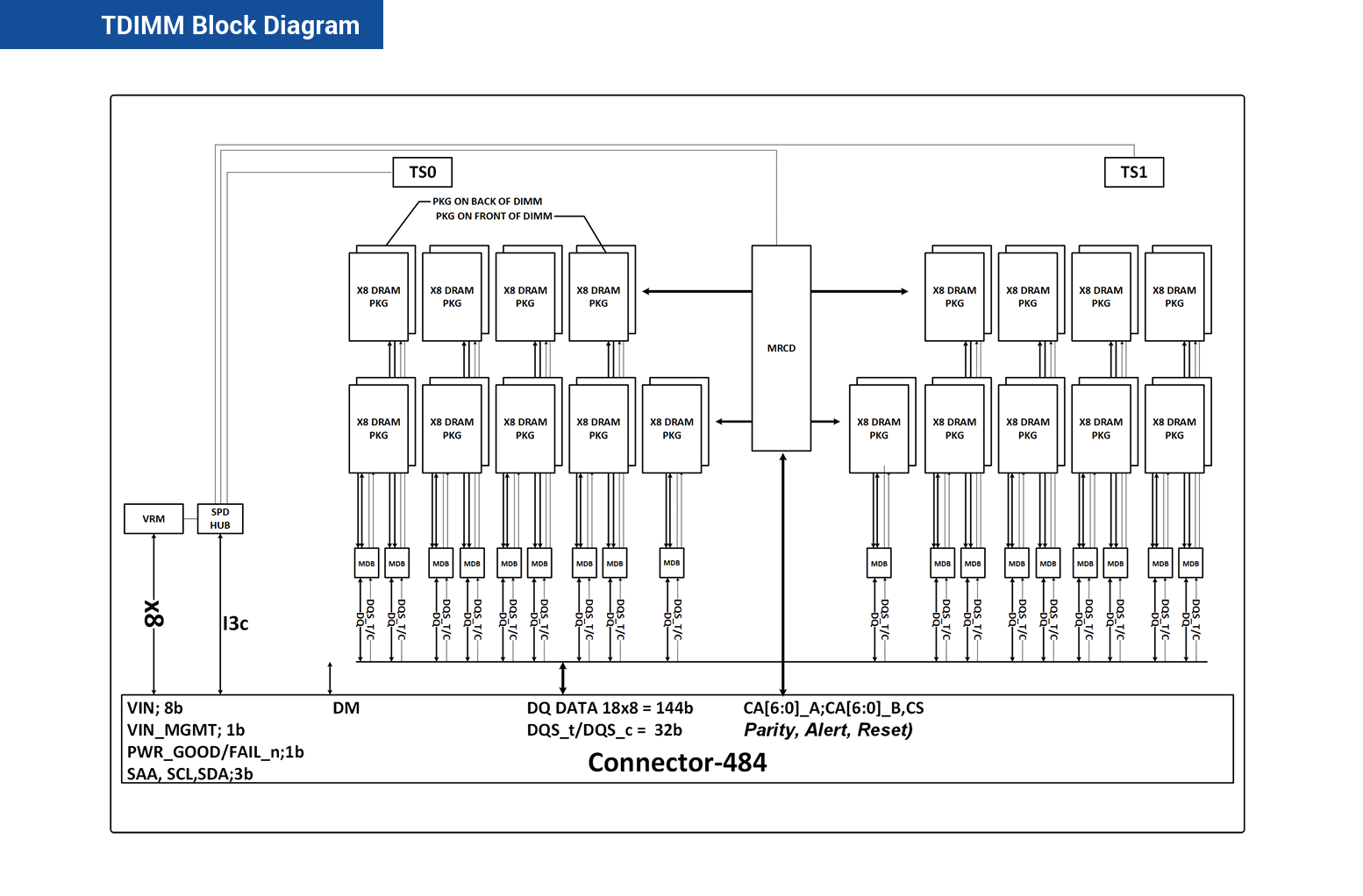

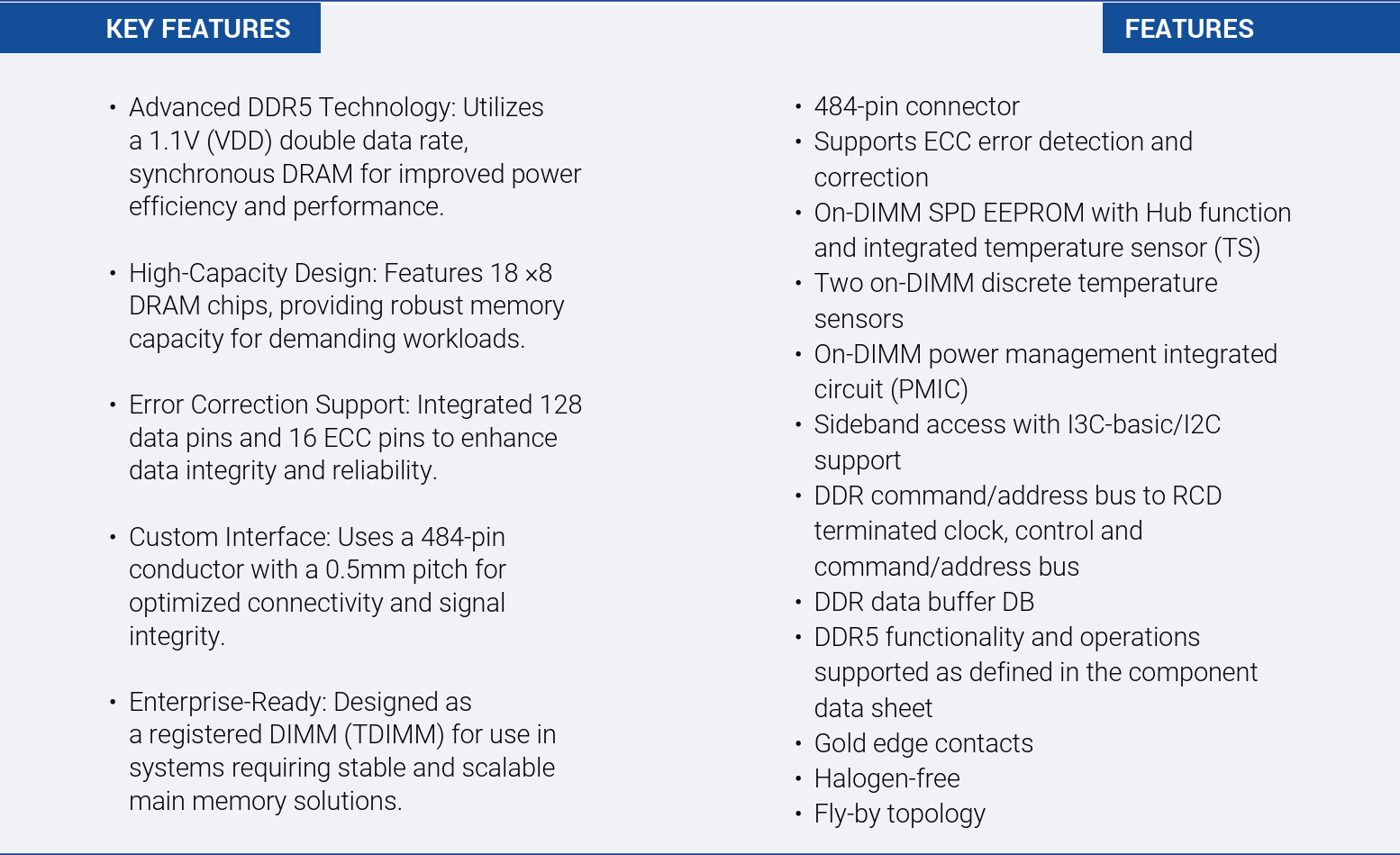

TDIMM 仍採與 DDR5 類似的模組尺寸,但由於資料位寬翻倍,因此需要全新腳位配置。官方表示,儘管訊號數量僅增加 38%,TDIMM 就能達成兩倍頻寬,並因使用更少的 DRAM 晶片,模組成本預估可降低約 10%。

Tachyum 執行長 Dr. Radoslav Danilak 表示,TDIMM 是推動較低成本 AI 的關鍵技術,將使得建立訓練於全人類書面知識上的模型變得可行。然而,目前 TDIMM 仍停留在規格公布階段,外界普遍認為其實際落地與產業接受度仍有待觀察。

來源

TDIMM:開源記憶體設計,較 DDR5 RDIMM 提升最高 5.5 倍頻寬

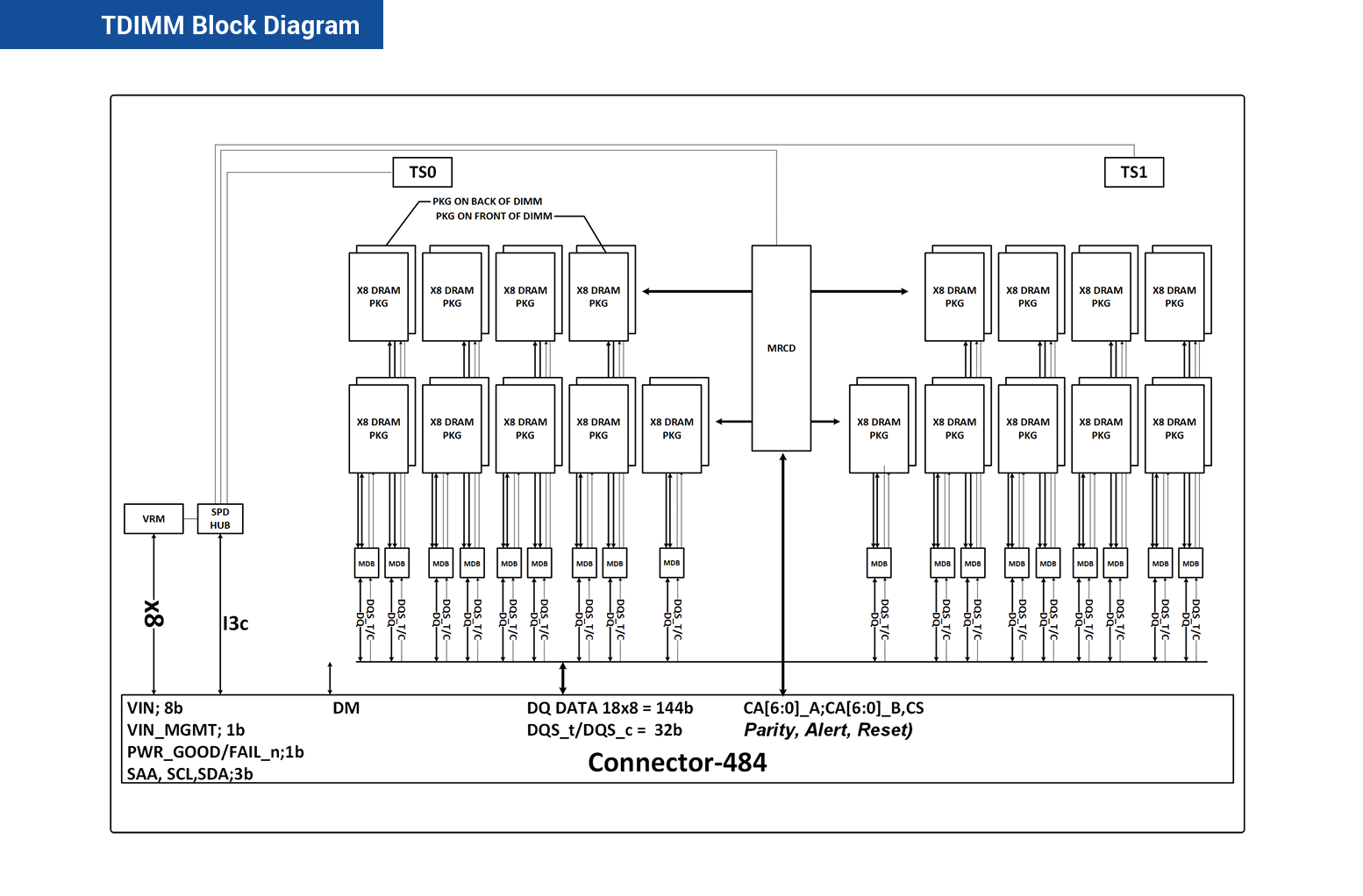

繼先前宣布 2nm Prodigy 與 Prodigy Ultimate 處理器後,Tachyum 進一步揭露 TDIMM 記憶體規格。根據官方資料,TDIMM 採用 DDR5 技術但重新設計模組架構,頻寬可從一般 RDIMM 的 51 GB/s 大幅提升至 281 GB/s,增幅約 5.5 倍。

TDIMM 的容量也隨不同外形尺寸而異:

- 標準高度:256 GB

- 加高版:512 GB

- 超高版(Extra Tall):最高 1 TB

TDIMM vs DDR5 RDIMM:腳位改變、資料寬度大幅增加

Tachyum 同時公布兩者的技術比較:| 項目 | DDR5 RDIMM | DDR5 TDIMM |

|---|---|---|

| 資料位元 | 64-bit | 128-bit |

| ECC | 16-bit | 16-bit |

| DQS | 40 | 36 |

| C/A | 14 | 14 |

| 控制訊號 | 16 | 16 |

| 腳位 | 288 pin | 484 pin |

TDIMM 仍採與 DDR5 類似的模組尺寸,但由於資料位寬翻倍,因此需要全新腳位配置。官方表示,儘管訊號數量僅增加 38%,TDIMM 就能達成兩倍頻寬,並因使用更少的 DRAM 晶片,模組成本預估可降低約 10%。

2028 年 TDIMM DDR6 版本頻寬上看 27 TB/s

Tachyum 也提出未來規劃,TDIMM 標準預期將持續演進,DDR6 版本頻寬上看 27 TB/s。相較之下,標準 DDR6 的提升幅度則從 DDR5 的 6.7 TB/s 增至約 13.5 TB/s。Tachyum:TDIMM 可大幅降低 AI 訓練成本,但仍需時間驗證

Tachyum 宣稱 TDIMM 在 AI 應用上的影響巨大,能顯著降低大型模型訓練所需的成本與能耗。例如其提到:- OpenAI 規模的資料中心成本可從 3 兆美元縮減至 270 億美元

- 電力需求從 25 萬 MW 降至 540 MW

Tachyum 執行長 Dr. Radoslav Danilak 表示,TDIMM 是推動較低成本 AI 的關鍵技術,將使得建立訓練於全人類書面知識上的模型變得可行。然而,目前 TDIMM 仍停留在規格公布階段,外界普遍認為其實際落地與產業接受度仍有待觀察。

來源