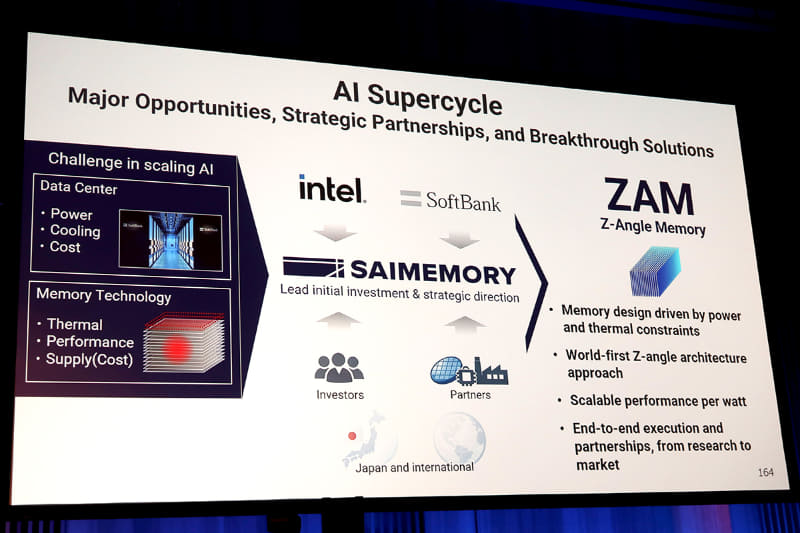

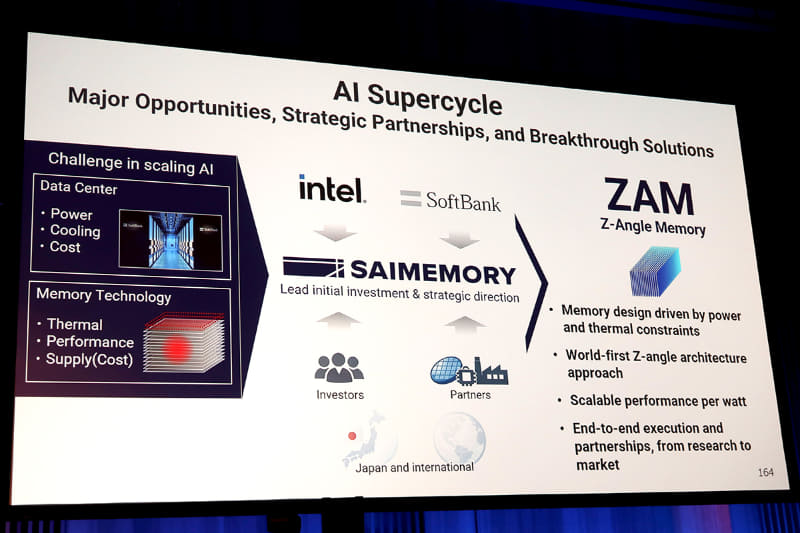

Intel 近期首度對外展示其參與的 Z-Angle Memory(ZAM)記憶體技術原型,這項方案被視為試圖從架構層面解決現行 HBM 在散熱與擴充性上的物理限制。相關內容出現在日本活動 Intel Connection Japan 2026 上,也讓原本只存在於研究與概念層面的 ZAM,首次有了具體樣貌。

ZAM 的核心概念是改變堆疊式記憶體的互連方式。傳統 HBM 依賴大量垂直 TSV(Through-Silicon Via)直通通孔,把訊號一路往下打洞傳遞;ZAM 則採用所謂的 Z-Angle(斜角)互連拓撲,在晶片堆疊內部以交錯、對角線方式傳遞連接。這種設計訴求為減少熱堆積、改善訊號路徑分佈,同時降低高密度垂直穿孔帶來的製程與良率壓力。

在活動簡報中,Intel 與合作方將重點放在熱與能效問題。HBM 在高頻寬優勢背後,堆疊高度與功耗密度也同步上升,導致散熱設計愈來愈吃緊。ZAM 的說法是,透過改變互連角度與路徑分佈,可讓熱源分散,而不是集中在垂直熱通道附近,理論上能讓封裝在高負載下更穩定。

目前對外流出的技術主張包括:功耗可比現有方案降低約 40–50%、互連結構更簡化、單顆模組容量有機會拉高到 512GB 等。不過這些數字仍屬早期階段的目標值,距離實際量產產品還有相當距離。

Intel 在這項專案中的角色也不是傳統意義上的記憶體製造商。公開資料顯示,其定位更偏向初期投資與策略層面參與,而技術開發則與 SoftBank 旗下 Saimemory 等單位合作。對 Intel 來說,這更像是在 HBM 主導的高頻寬記憶體戰場旁邊,押下一張下一代堆疊架構的長期選擇權。

整體來看,ZAM 現階段還談不上要取代 HBM,比較像是針對未來 AI 與高效能運算持續推高記憶體頻寬與容量時,提前佈局的一條新路線。它能不能真的在製程、成本與封裝整合上站得住腳,還得等後續更實際的晶片與系統級驗證出來,才會有答案。

ZAM 的核心概念是改變堆疊式記憶體的互連方式。傳統 HBM 依賴大量垂直 TSV(Through-Silicon Via)直通通孔,把訊號一路往下打洞傳遞;ZAM 則採用所謂的 Z-Angle(斜角)互連拓撲,在晶片堆疊內部以交錯、對角線方式傳遞連接。這種設計訴求為減少熱堆積、改善訊號路徑分佈,同時降低高密度垂直穿孔帶來的製程與良率壓力。

在活動簡報中,Intel 與合作方將重點放在熱與能效問題。HBM 在高頻寬優勢背後,堆疊高度與功耗密度也同步上升,導致散熱設計愈來愈吃緊。ZAM 的說法是,透過改變互連角度與路徑分佈,可讓熱源分散,而不是集中在垂直熱通道附近,理論上能讓封裝在高負載下更穩定。

目前對外流出的技術主張包括:功耗可比現有方案降低約 40–50%、互連結構更簡化、單顆模組容量有機會拉高到 512GB 等。不過這些數字仍屬早期階段的目標值,距離實際量產產品還有相當距離。

Intel 在這項專案中的角色也不是傳統意義上的記憶體製造商。公開資料顯示,其定位更偏向初期投資與策略層面參與,而技術開發則與 SoftBank 旗下 Saimemory 等單位合作。對 Intel 來說,這更像是在 HBM 主導的高頻寬記憶體戰場旁邊,押下一張下一代堆疊架構的長期選擇權。

整體來看,ZAM 現階段還談不上要取代 HBM,比較像是針對未來 AI 與高效能運算持續推高記憶體頻寬與容量時,提前佈局的一條新路線。它能不能真的在製程、成本與封裝整合上站得住腳,還得等後續更實際的晶片與系統級驗證出來,才會有答案。