本週將舉行 ISSCC 2022(IEEE 國際固態電路會議),AMD 將在會議上分享其 3D V-Cache 設計的更多細節。AMD 此前已經在 CES 2022 上,推出了採用 3D 垂直快取技術的 Zen 3 架構桌面處理器,即 Ryzen 7 5800X3D,為每個 CCD 帶來額外的 64MB 7nm SRAM 快取,使 L3 快取容量由32MB增加到了96MB。

據報導,3D V-Cache 由多個 8MB 的“slices”組成,這些“slices”具有1024個與單個 CPU 內核接觸的接口,CCX 和 3D V-Cache 之間共有8192個連接點,允許每片“slices”在全雙工模式下傳輸帶寬達到了 2TB/s。儘管沒有集成在 CCX 上,但很可能與本身 L3 快取的速度一致。據稱 AMD 還通過多種方式改進了 Ryzen 7 5800X3D 的設計,以降低功耗並提高頻率。AMD 至今沒有確認 Ryzen 7 5800X3D 什麼時候上市,不過在 Zen 4 架構的 Ryzen 7000 系列到來之前,這是為數不多與 Intel Alder Lake 12代的對抗產品。

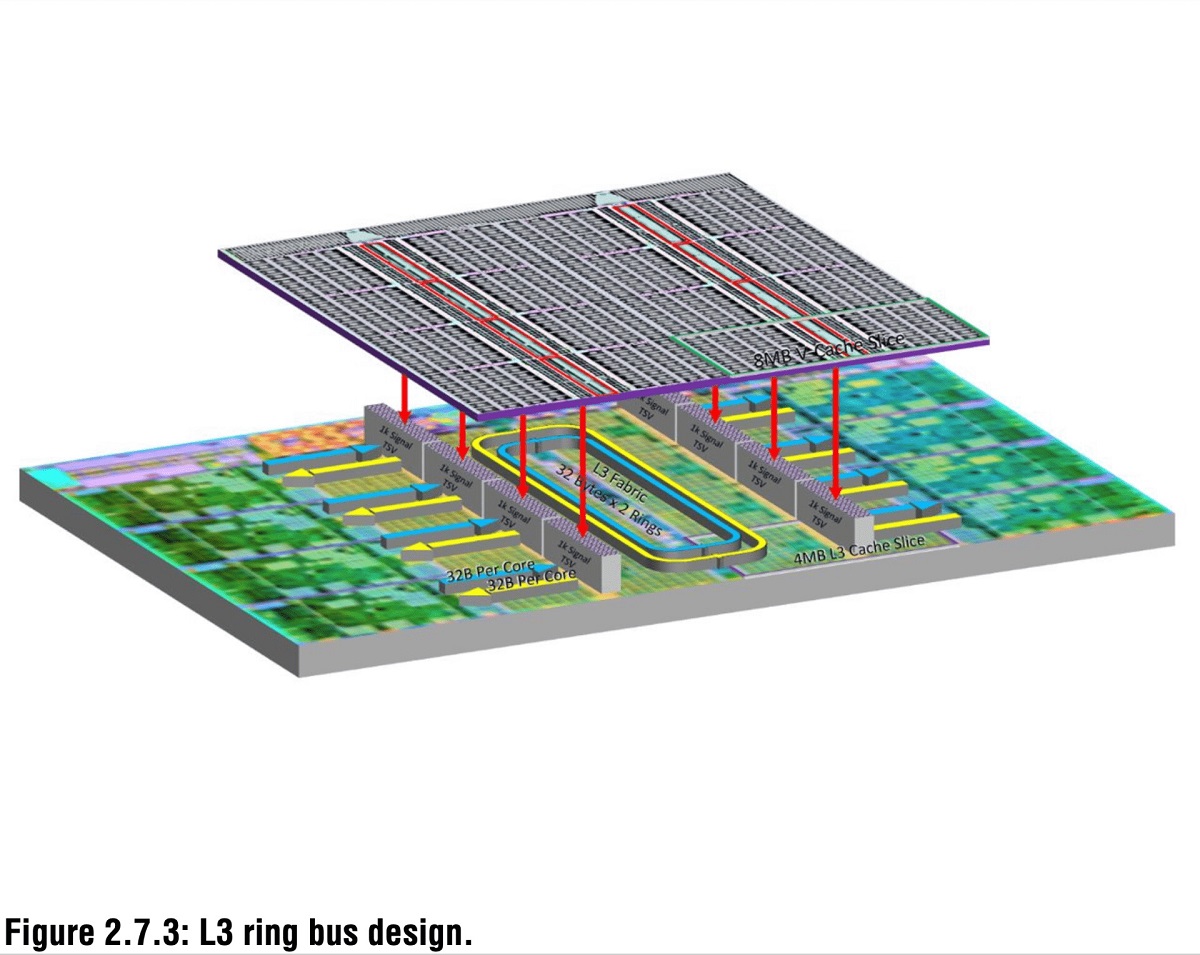

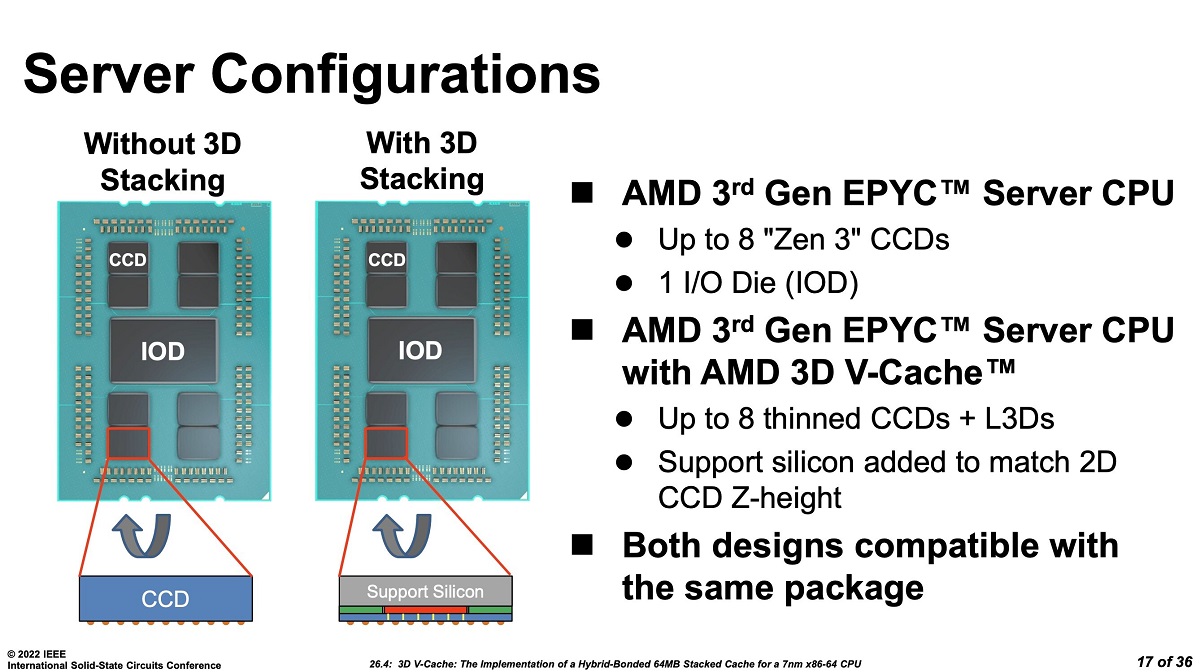

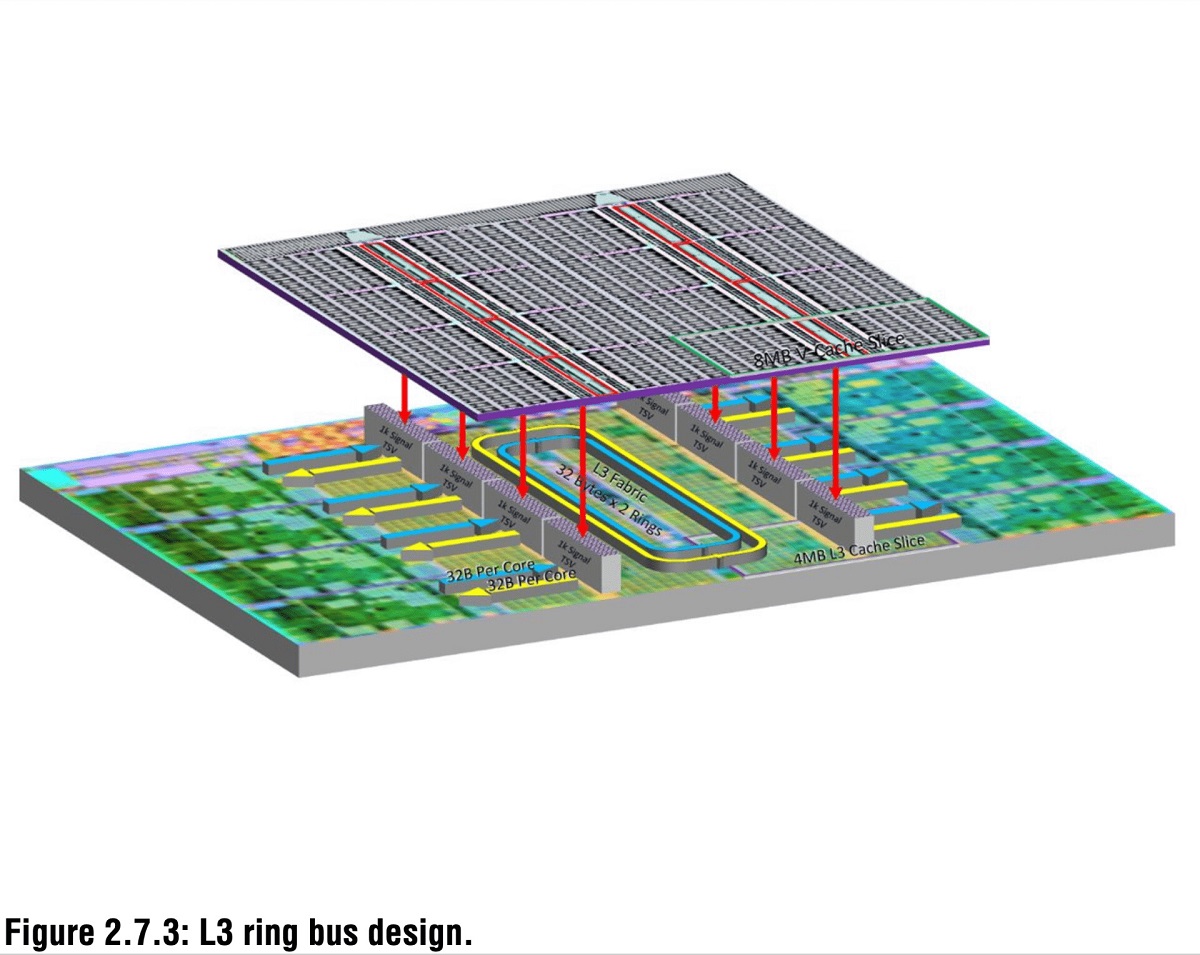

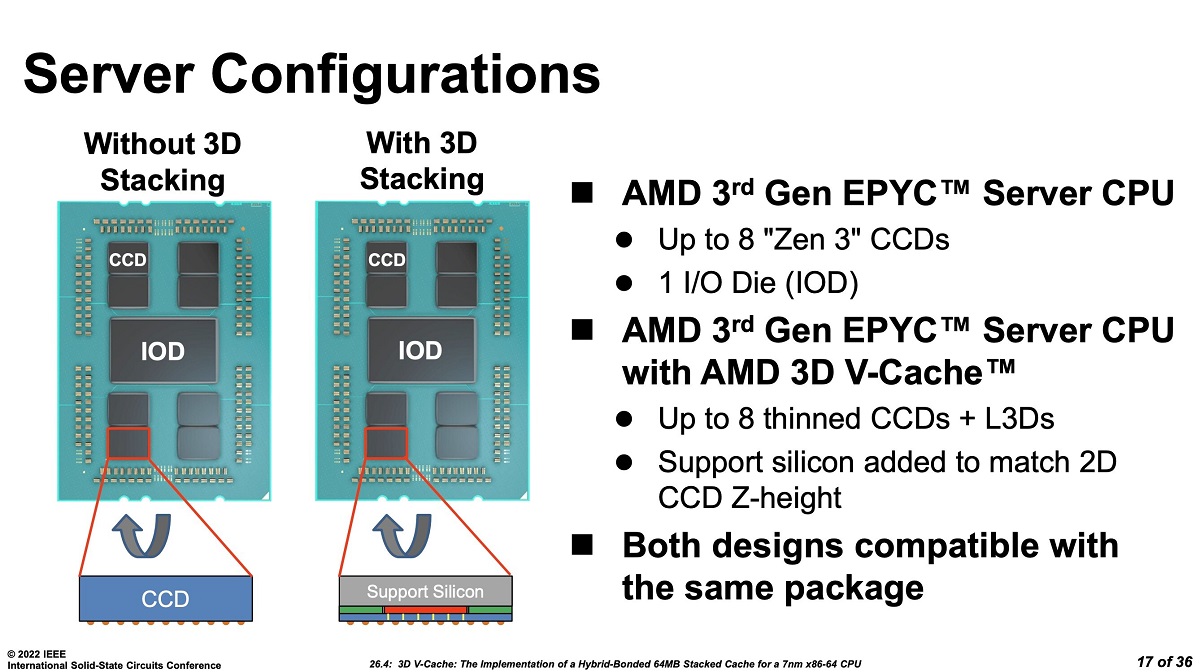

根據 AMD 演示文件內容,顯示 3D V-Cache 的 SRAM 採用了台積電 N7 製程製造,整體尺寸為41mm2,通過兩個額外的 CCD 結構支撐以協助散熱。為了能裝入相同的封裝中,AMD 還將原有的 CCD 削薄。為了讓處理器的每個內核與 3D V-Cache 連結通信,AMD 在 L3 上實現了共享環形總線設計,整個 L3 快取可用於每個內核。

去年 AMD 曾介紹,這項 3D 晶片堆疊技術是基於台積電的 SoIC 技術,將兩個晶片被銑成一個完美的平面,底層 CCX 與頂層 L3 快取之間是一個完美的對齊,TSV 通道可以在沒有任何類型的粘合材料的情況下進行匹配。為了實現這個操作,AMD 並將 CCX 翻轉(由面向頂部改為面向底部),然後削去了頂部95%的矽,再將 3D 垂直快取晶片安裝在上面。

來源

據報導,3D V-Cache 由多個 8MB 的“slices”組成,這些“slices”具有1024個與單個 CPU 內核接觸的接口,CCX 和 3D V-Cache 之間共有8192個連接點,允許每片“slices”在全雙工模式下傳輸帶寬達到了 2TB/s。儘管沒有集成在 CCX 上,但很可能與本身 L3 快取的速度一致。據稱 AMD 還通過多種方式改進了 Ryzen 7 5800X3D 的設計,以降低功耗並提高頻率。AMD 至今沒有確認 Ryzen 7 5800X3D 什麼時候上市,不過在 Zen 4 架構的 Ryzen 7000 系列到來之前,這是為數不多與 Intel Alder Lake 12代的對抗產品。

根據 AMD 演示文件內容,顯示 3D V-Cache 的 SRAM 採用了台積電 N7 製程製造,整體尺寸為41mm2,通過兩個額外的 CCD 結構支撐以協助散熱。為了能裝入相同的封裝中,AMD 還將原有的 CCD 削薄。為了讓處理器的每個內核與 3D V-Cache 連結通信,AMD 在 L3 上實現了共享環形總線設計,整個 L3 快取可用於每個內核。

去年 AMD 曾介紹,這項 3D 晶片堆疊技術是基於台積電的 SoIC 技術,將兩個晶片被銑成一個完美的平面,底層 CCX 與頂層 L3 快取之間是一個完美的對齊,TSV 通道可以在沒有任何類型的粘合材料的情況下進行匹配。為了實現這個操作,AMD 並將 CCX 翻轉(由面向頂部改為面向底部),然後削去了頂部95%的矽,再將 3D 垂直快取晶片安裝在上面。

來源