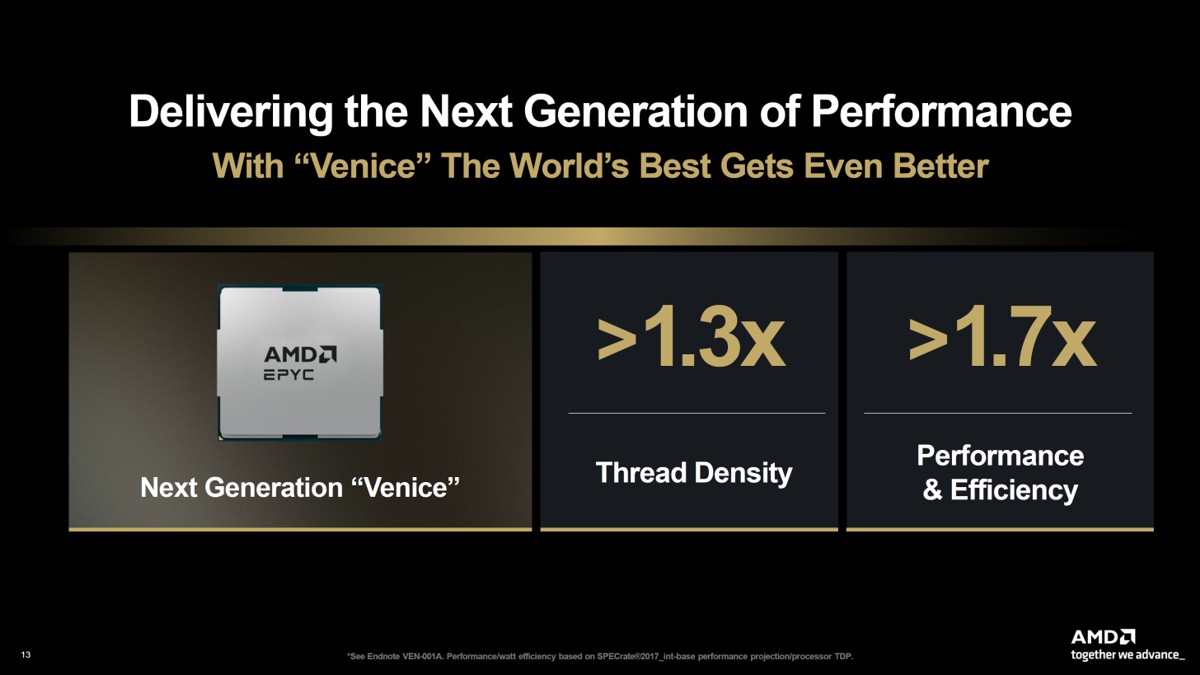

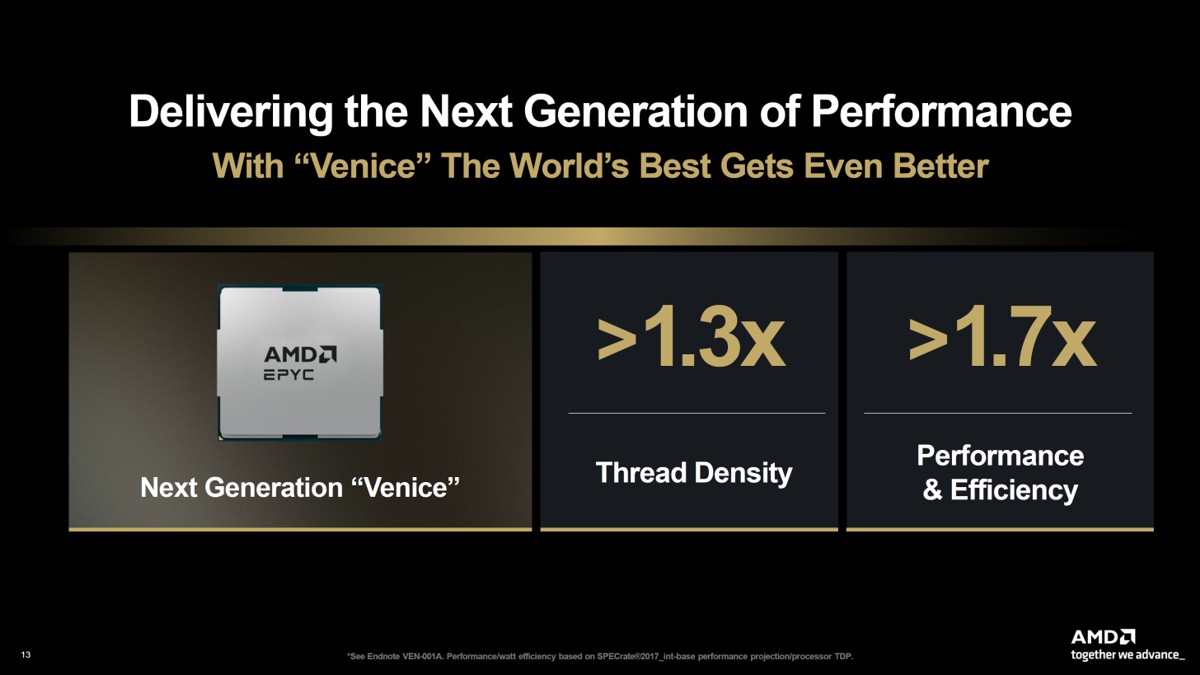

近日,AMD 釋出一份名為《Performance Monitor Countersfor AMD Family 1Ah Model 50h57h Processors》的技術文件,內容首度揭露了 Zen 6 架構處理器的多項設計細節,其中也包含代號 「Venice」的 EPYC 伺服器處理器。簡單來說,Zen 6 並非 Zen 5 的延伸進化,而是採用全新設計思維、從底層重新打造的一代架構。

其實 AMD 先前已經相當概略地提過 Zen 6 的部分方向,包括最高可達 256 核心,並採用台積電(TSMC)新一代 2nm 製程。而這次公開的開發者文件則進一步確認,Zen 6 並不是 Zen 4 / Zen 5 的漸進式升級,而是導入 全面翻新的高吞吐量寬架構,具備 8-wide 指令發射與排程引擎,並持續支援同步多執行緒(SMT)。

在核心設計上,Zen 6 也新增多種專用效能計數器,用來追蹤像是排程視窗閒置、後端管線阻塞等狀況,提供更細緻的效能分析能力。

依照 AMD 的架構規劃,兩條硬體執行緒會動態競爭同一個排程資源池。在相同時脈下,Zen 6 的單執行緒效能可能不會像蘋果採用 9-wide 架構那樣突出,但在特定負載情境中,這類設計能確保整體效能表現維持在非常高的水準,也反映出 AMD 在 Zen 6 上著重的關鍵,正是單一時脈能同時處理更多指令與 SMT 執行緒的資源分配與排程設計。

指令集方面,Zen 6 延續對 512 位元 AVX-512 的支援,並相容 FP64 / FP32 / FP16 / BF16 等浮點格式,同時涵蓋 FMA / MAC 運算,以及浮點與整數混合向量運算(如 VNNI / AES / SHA)。文件中也提到,Zen 6 能夠提供持續性的高 512 位元吞吐量,效能表現甚至需要合併多個效能計數器才能準確測量,顯示其單週期向量運算能力已高到傳統量測方式難以完整反映,必須導入新的監控介面。

整體而言,Zen 6 是 AMD 首款完全以資料中心應用為核心,從零開始設計的微架構。至於未來在桌機或行動平台上的實際表現,仍有待後續產品與測試進一步觀察。

來源

其實 AMD 先前已經相當概略地提過 Zen 6 的部分方向,包括最高可達 256 核心,並採用台積電(TSMC)新一代 2nm 製程。而這次公開的開發者文件則進一步確認,Zen 6 並不是 Zen 4 / Zen 5 的漸進式升級,而是導入 全面翻新的高吞吐量寬架構,具備 8-wide 指令發射與排程引擎,並持續支援同步多執行緒(SMT)。

在核心設計上,Zen 6 也新增多種專用效能計數器,用來追蹤像是排程視窗閒置、後端管線阻塞等狀況,提供更細緻的效能分析能力。

依照 AMD 的架構規劃,兩條硬體執行緒會動態競爭同一個排程資源池。在相同時脈下,Zen 6 的單執行緒效能可能不會像蘋果採用 9-wide 架構那樣突出,但在特定負載情境中,這類設計能確保整體效能表現維持在非常高的水準,也反映出 AMD 在 Zen 6 上著重的關鍵,正是單一時脈能同時處理更多指令與 SMT 執行緒的資源分配與排程設計。

指令集方面,Zen 6 延續對 512 位元 AVX-512 的支援,並相容 FP64 / FP32 / FP16 / BF16 等浮點格式,同時涵蓋 FMA / MAC 運算,以及浮點與整數混合向量運算(如 VNNI / AES / SHA)。文件中也提到,Zen 6 能夠提供持續性的高 512 位元吞吐量,效能表現甚至需要合併多個效能計數器才能準確測量,顯示其單週期向量運算能力已高到傳統量測方式難以完整反映,必須導入新的監控介面。

整體而言,Zen 6 是 AMD 首款完全以資料中心應用為核心,從零開始設計的微架構。至於未來在桌機或行動平台上的實際表現,仍有待後續產品與測試進一步觀察。

來源