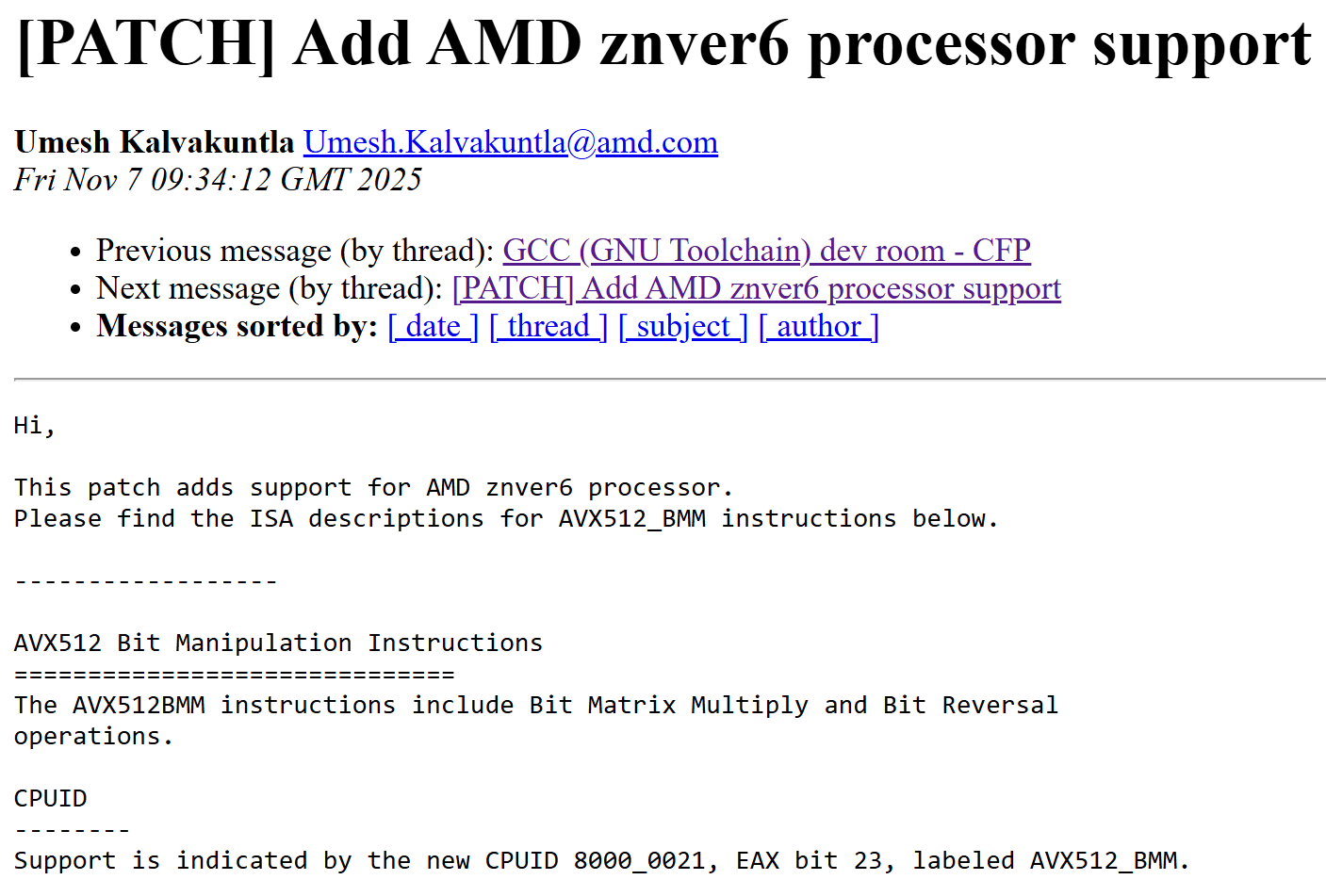

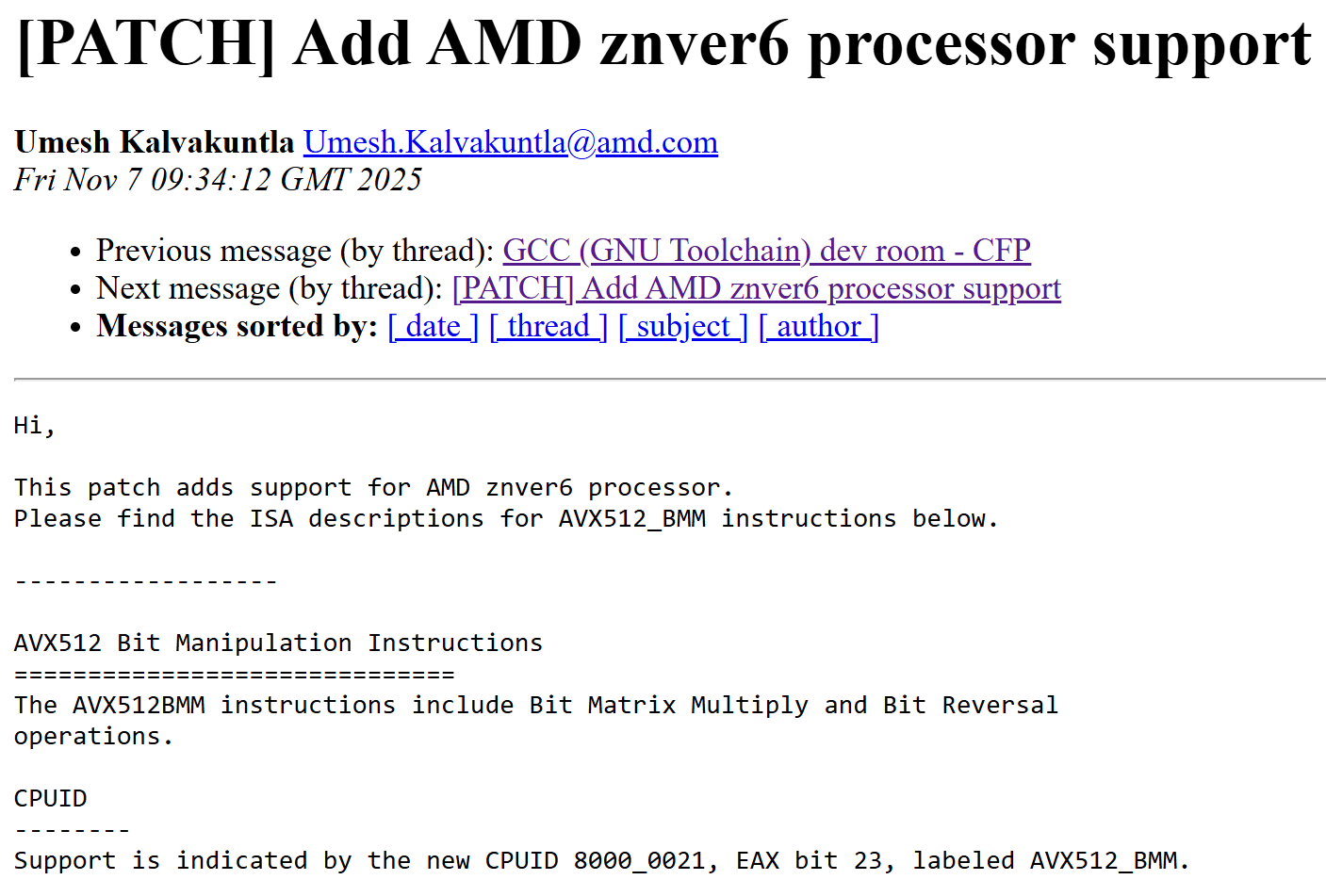

GCC 編譯器近期加入了「znver6」的支援,間接揭露了 AMD 下一代 Zen 6 架構的部分 ISA(指令集)資訊。

本次新增的 Zen 6 指令集包含:

AMD 目前的 Zen 系列已支援 AVX-512,而 Zen 6 進一步加入 FP16 浮點運算與 VNNI INT8,可提升 AI、推論與特定高效能運算的表現。

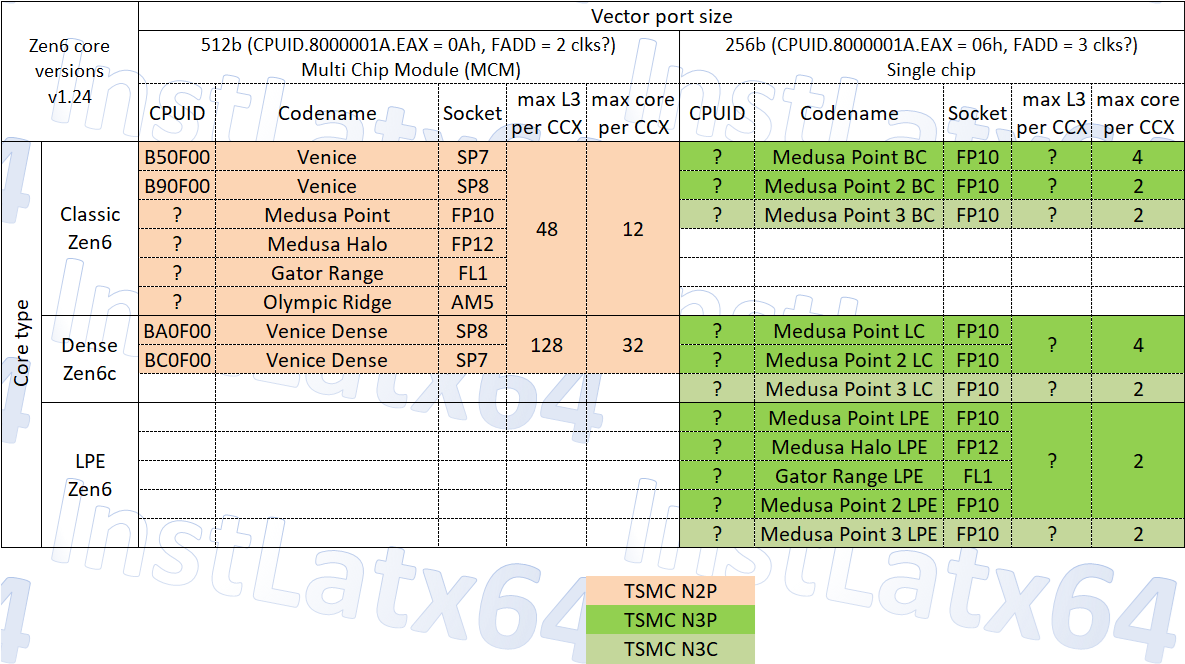

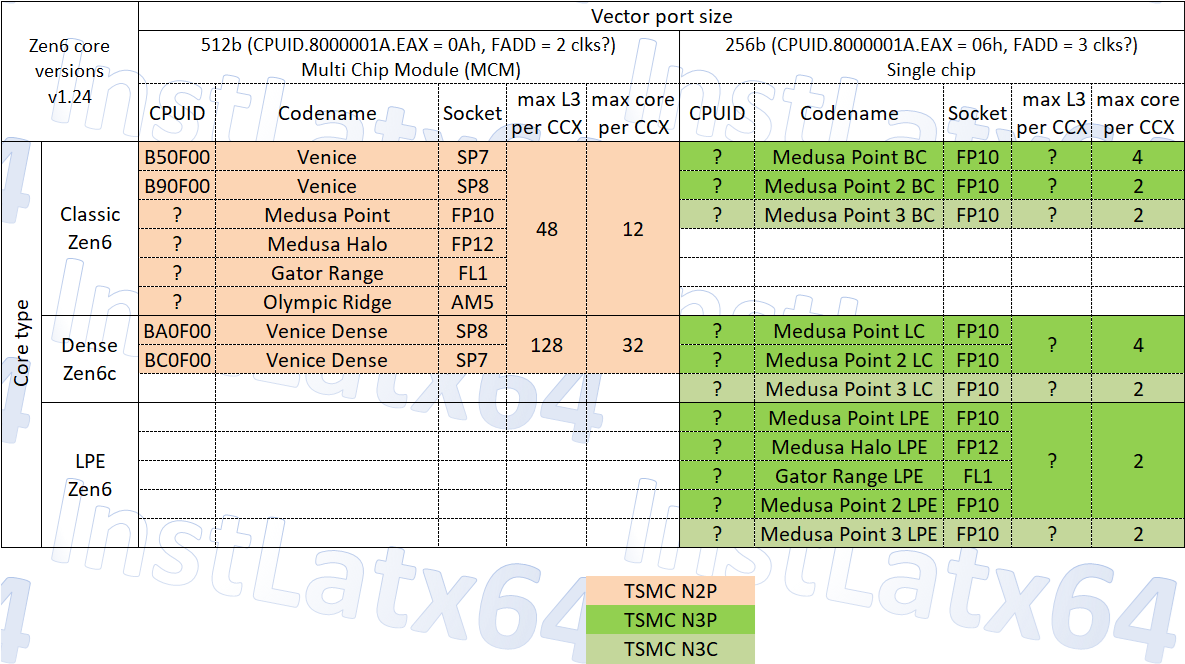

此外,@InstLatX64 也發現新的 Zen 6 CPUID「B80F00」,應代表 Zen 6 系列中的其中一個家族。

Zen 6 預期產品線

現階段的資訊顯示,Zen 6 會延續「Venice」伺服器系列,並分為 Classic 與 Dense 兩種版本:

多晶片(MCM)產品將採用 台積電 N2P 製程,單晶片(monolithic)APU 則預計使用 N3P / N3C。

AMD 將在數天後的財務說明會中釋出更多 Zen 6 的方向,不過大部分公開可能仍要等到 2026 年初的 CES 2026。

來源

本次新增的 Zen 6 指令集包含:

- AVX512_FP16

- AVX_NE_CONVERT

- AVX_IFMA

- AVX_VNNI_INT8

AMD 目前的 Zen 系列已支援 AVX-512,而 Zen 6 進一步加入 FP16 浮點運算與 VNNI INT8,可提升 AI、推論與特定高效能運算的表現。

此外,@InstLatX64 也發現新的 Zen 6 CPUID「B80F00」,應代表 Zen 6 系列中的其中一個家族。

Zen 6 預期產品線

現階段的資訊顯示,Zen 6 會延續「Venice」伺服器系列,並分為 Classic 與 Dense 兩種版本:

- Classic 系列:每個 CCX 提供最多 12 核心

- Dense 系列:每個 CCX 提供最多 32 核心,L3 高達 128 MB

- 最高規格:最多 8 個 CCX、合計 256 核心、1GB L3 Cache

- Olympic Ridge(AM5):最高 24 核心、48 執行緒

- Gator Range

- Medusa Point

- Medusa Halo

多晶片(MCM)產品將採用 台積電 N2P 製程,單晶片(monolithic)APU 則預計使用 N3P / N3C。

AMD 將在數天後的財務說明會中釋出更多 Zen 6 的方向,不過大部分公開可能仍要等到 2026 年初的 CES 2026。

來源