近日有新爆料指出,AMD 下一代 RDNA 5 / UDNA 架構顯示卡,可能會推出至少四種不同晶片配置,最高階版本將搭載多達 96 個計算單元(CU)。

最初的相關推測可追溯到 7 月,由知名爆料者 Kepler_L2 在 Anandtech 論壇分享,他過去曾多次準確透露 AMD 與 Intel 產品訊息,以及尚未上市的遊戲主機細節。這次則公開了多張疑似 RDNA 5 / UDNA 系列 GPU 方塊圖。

最高階版本 96 CU,512-bit 記憶體匯流排

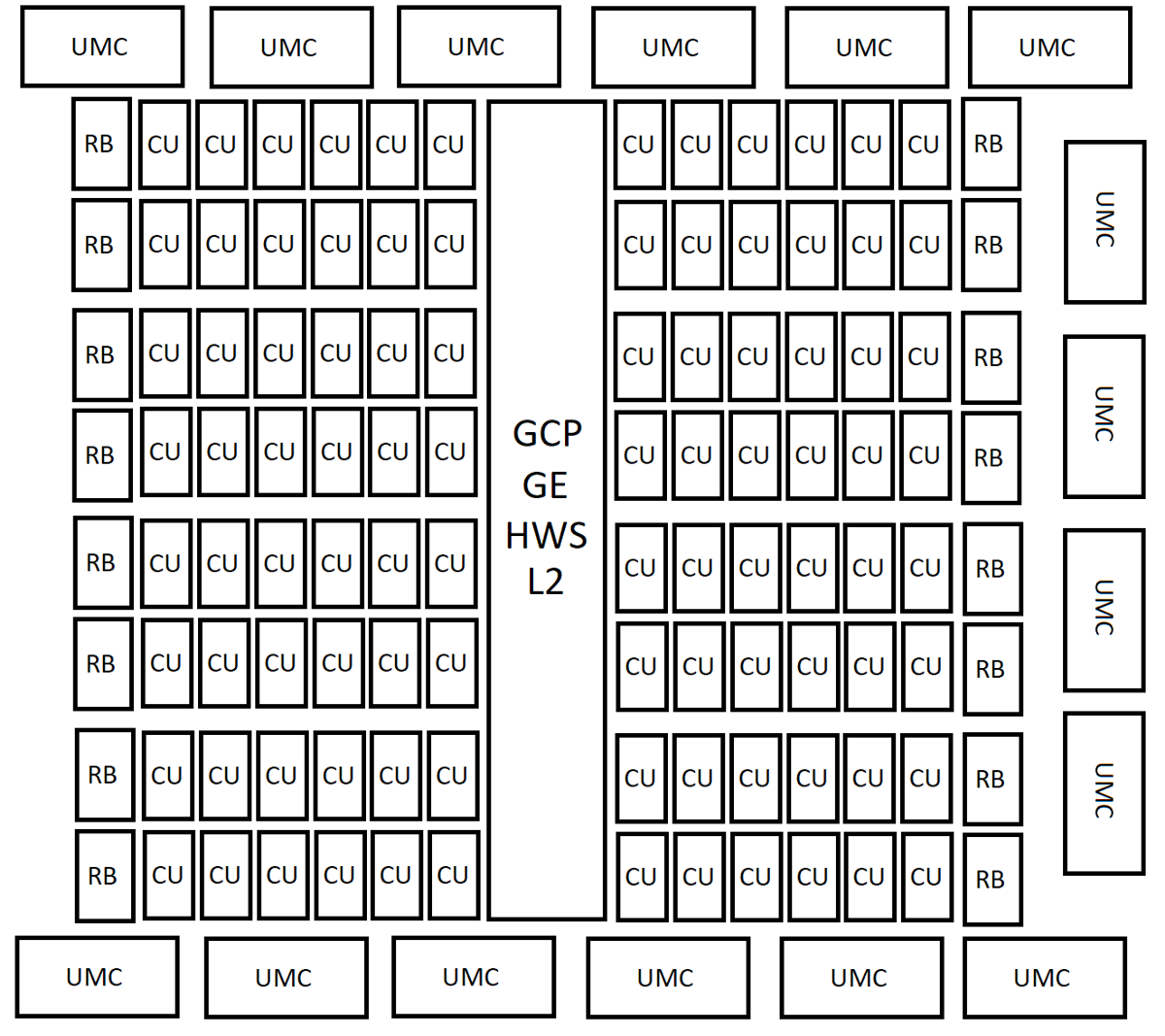

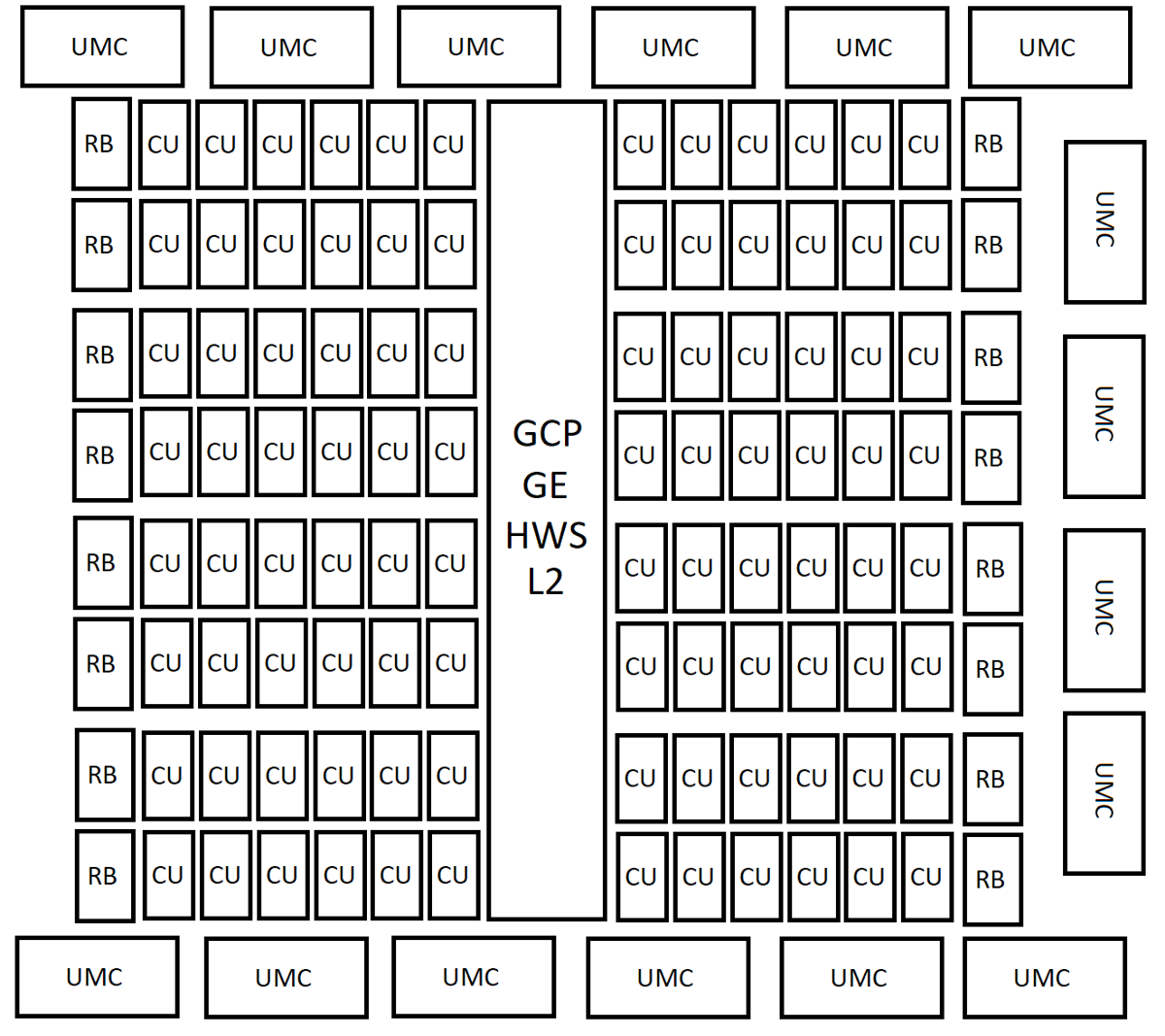

旗艦核心設計包含 8 個 Shader Arrays,每個 Array 內建 2 個 Shader Engine,合計 16 個 Shader Engine。每個 Engine 配置 6 個 CU,因此總數達到 96 CU。

此外,每個 Shader Engine 擁有獨立的 Render Backend,並與中央 SoC 區塊相連,該區塊包含 圖形命令處理器、圖形引擎、硬體排程器(HWS)與 L2 快取。

記憶體部分則有 16 組 32-bit 控制器(總計 512-bit 匯流排),並可能搭載 高達 128MB 的 Infinity Cache。

中階版本 40 CU,192-bit 匯流排

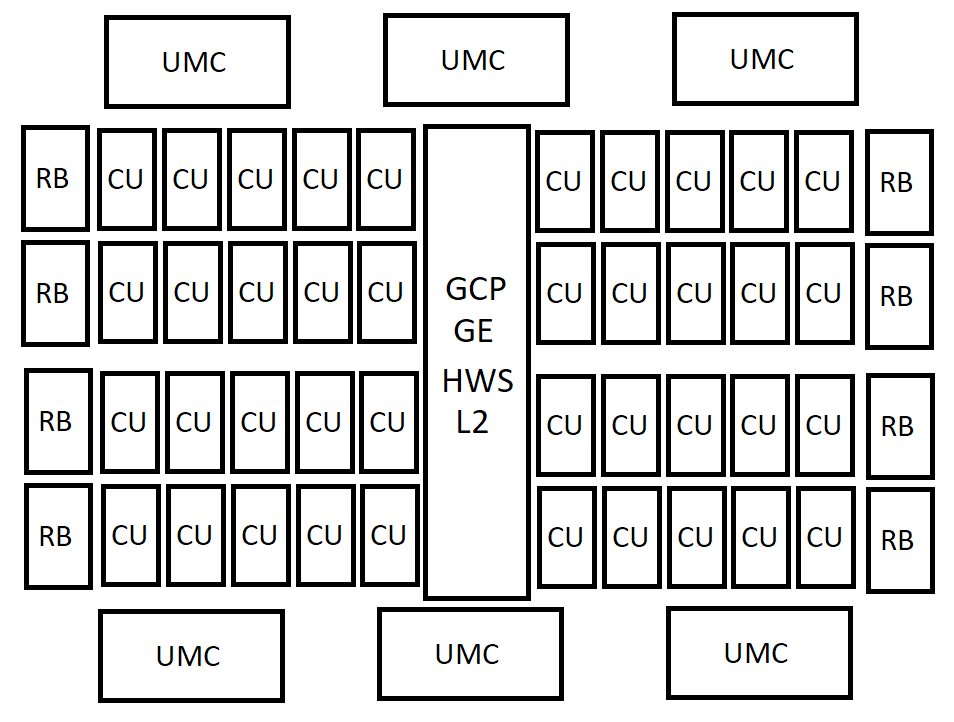

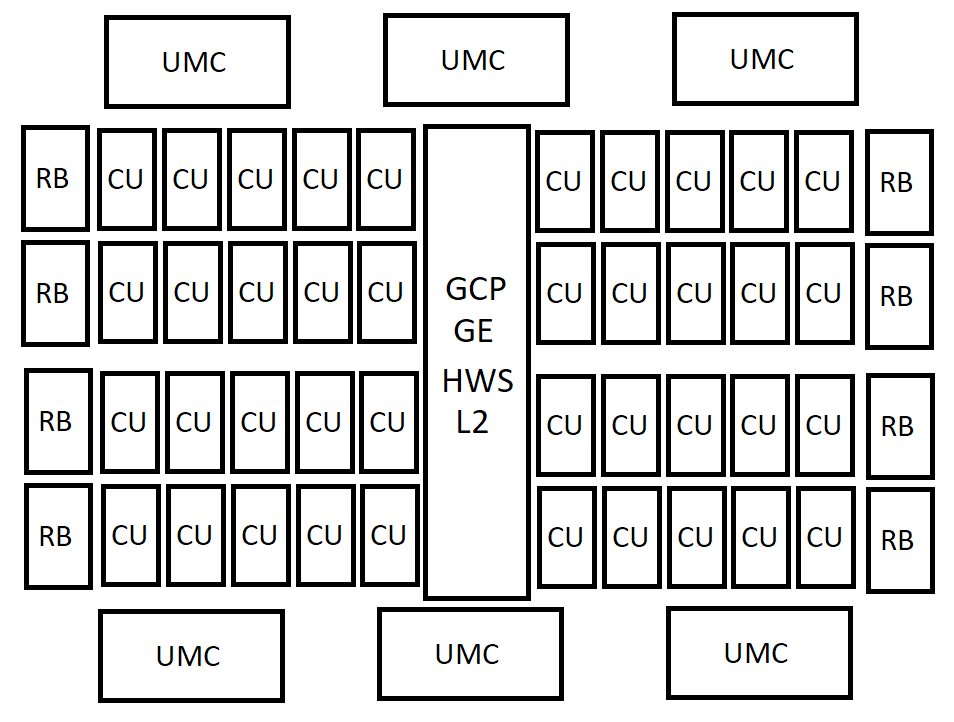

往下則是 40 CU 版本,設計上採用 8 個 Shader Engine、每個含 5 CU,合計 40 CU。

其搭載 6 組記憶體控制器,組成 192-bit 匯流排,並可能擁有 48MB Infinity Cache。由於 RDNA 5 架構具備高度模組化設計,AMD 預期會根據此核心衍生出多種型號。

入門版本 24 CU 與 12 CU

入門級晶片則涵蓋 24 CU 與 12 CU 兩種:

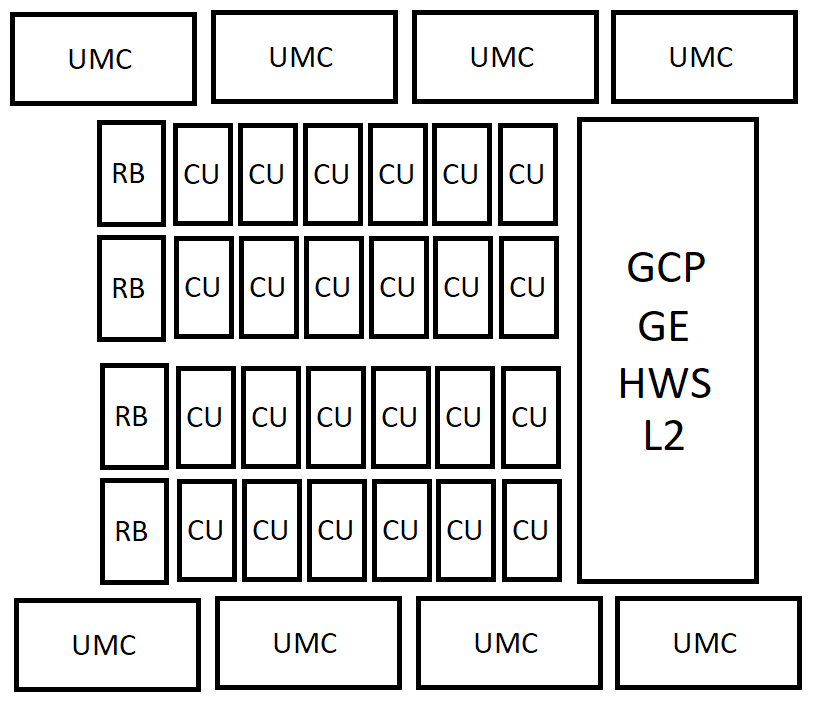

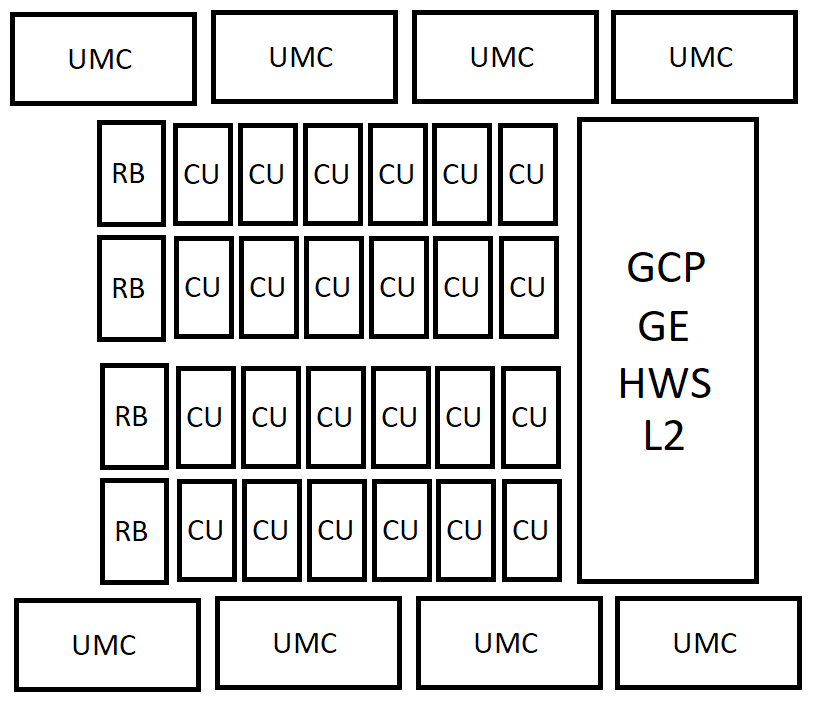

24 CU:由 4 個 Shader Engines(每個 6 CU)組成,搭配 8 組記憶體控制器,匯流排可能為 128-bit 或 256-bit,不過後者機率較低。

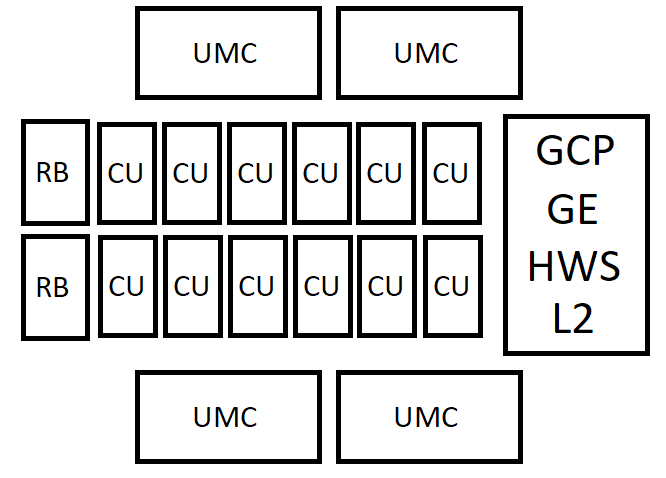

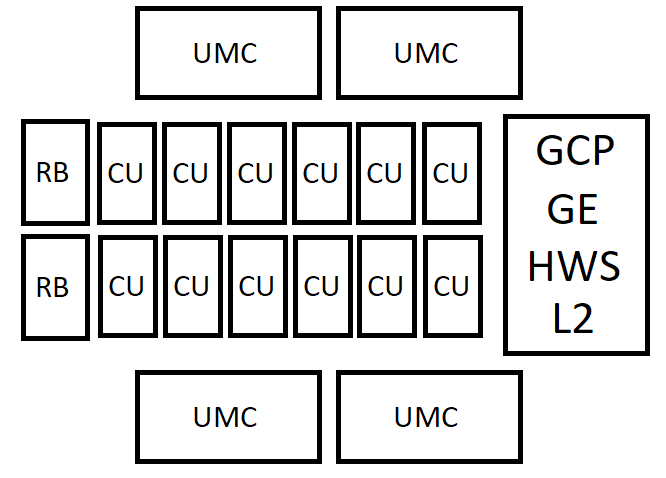

12 CU:最小版本,具備 2 個 Shader Engines(共 12 CU),配備 4 組控制器,匯流排可能為 64-bit 或 128-bit,Infinity Cache 則在 16–32MB 之間。

來源也提到,未來每個 RDNA 5 的 CU 幾乎等同於一個 RDNA 4 的 WGP,若以此推算,核心數量可能呈現翻倍效應。

同時,AMD 在資料中心架構 CDNA 5(MI400 系列) 已經擴增快取容量,若該設計下放至消費級,RDNA 5 / UDNA 有望進一步強化本地快取。由於新架構可能統一 Radeon 與 Instinct 的設計,因此取名為 UDNA。

據傳 RDNA 5 / UDNA 產品將於 2026 年第二季進入量產。屆時 NVIDIA 可能會推出 RTX 50 SUPER 系列,而 Intel 也預計發表 BMG-G31 Big Battlemage 系列顯卡。

最初的相關推測可追溯到 7 月,由知名爆料者 Kepler_L2 在 Anandtech 論壇分享,他過去曾多次準確透露 AMD 與 Intel 產品訊息,以及尚未上市的遊戲主機細節。這次則公開了多張疑似 RDNA 5 / UDNA 系列 GPU 方塊圖。

最高階版本 96 CU,512-bit 記憶體匯流排

旗艦核心設計包含 8 個 Shader Arrays,每個 Array 內建 2 個 Shader Engine,合計 16 個 Shader Engine。每個 Engine 配置 6 個 CU,因此總數達到 96 CU。

此外,每個 Shader Engine 擁有獨立的 Render Backend,並與中央 SoC 區塊相連,該區塊包含 圖形命令處理器、圖形引擎、硬體排程器(HWS)與 L2 快取。

記憶體部分則有 16 組 32-bit 控制器(總計 512-bit 匯流排),並可能搭載 高達 128MB 的 Infinity Cache。

中階版本 40 CU,192-bit 匯流排

往下則是 40 CU 版本,設計上採用 8 個 Shader Engine、每個含 5 CU,合計 40 CU。

其搭載 6 組記憶體控制器,組成 192-bit 匯流排,並可能擁有 48MB Infinity Cache。由於 RDNA 5 架構具備高度模組化設計,AMD 預期會根據此核心衍生出多種型號。

入門版本 24 CU 與 12 CU

入門級晶片則涵蓋 24 CU 與 12 CU 兩種:

24 CU:由 4 個 Shader Engines(每個 6 CU)組成,搭配 8 組記憶體控制器,匯流排可能為 128-bit 或 256-bit,不過後者機率較低。

12 CU:最小版本,具備 2 個 Shader Engines(共 12 CU),配備 4 組控制器,匯流排可能為 64-bit 或 128-bit,Infinity Cache 則在 16–32MB 之間。

來源也提到,未來每個 RDNA 5 的 CU 幾乎等同於一個 RDNA 4 的 WGP,若以此推算,核心數量可能呈現翻倍效應。

同時,AMD 在資料中心架構 CDNA 5(MI400 系列) 已經擴增快取容量,若該設計下放至消費級,RDNA 5 / UDNA 有望進一步強化本地快取。由於新架構可能統一 Radeon 與 Instinct 的設計,因此取名為 UDNA。

據傳 RDNA 5 / UDNA 產品將於 2026 年第二季進入量產。屆時 NVIDIA 可能會推出 RTX 50 SUPER 系列,而 Intel 也預計發表 BMG-G31 Big Battlemage 系列顯卡。