據 DRAMeXchange 報導,DRAM 市場供給過剩導致價格不斷下跌,DRAM 廠雖然盡量減產但仍然無法讓價格明顯止跌,維持獲利的唯一方法就是微縮製程來降低單位生產成本。不過,DRAM 製程向 1z nm 或 1α nm 製程推進的難度愈來愈高,隨著 EUV 量產技術獲得突破,或可有效降低 DRAM 成本。

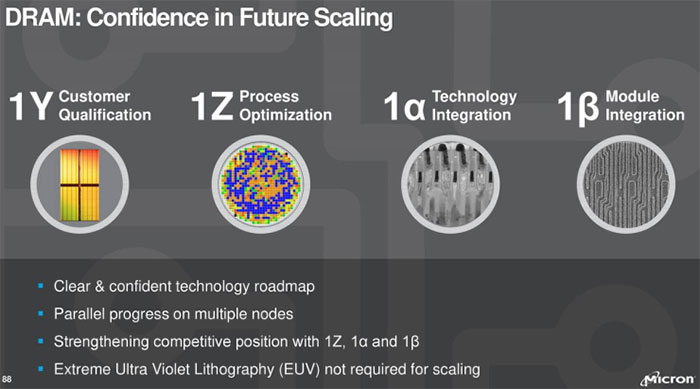

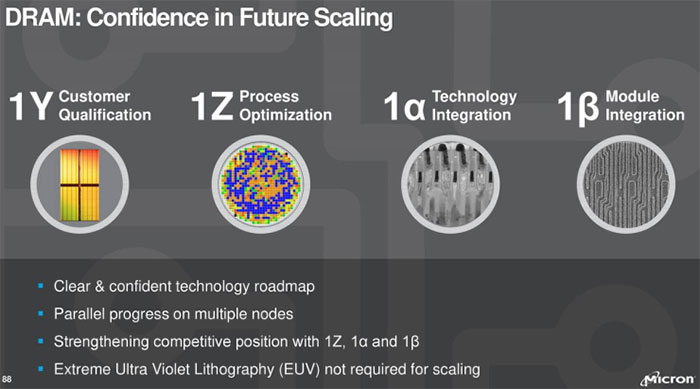

據悉,三星預期在今年11月開始量產採用 EUV 技術的 1z nm DRAM,量產初期將與三星晶圓代工共享 EUV 設備,初期使用量雖不大,但卻等於宣示 DRAM 光罩微影技術會朝 EUV 方向發展。至於 SK Hynix 及 Micron 也已表明開始評估採用 EUV 技術,業界預期將可能在 1α nm 或 1β nm 世代開始導入。

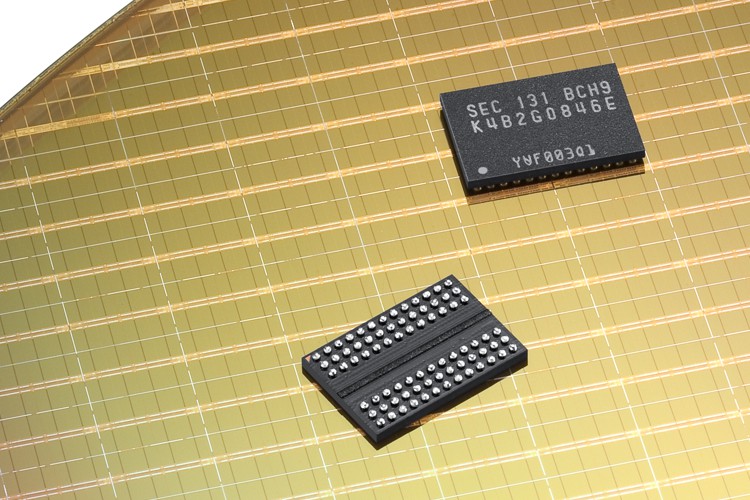

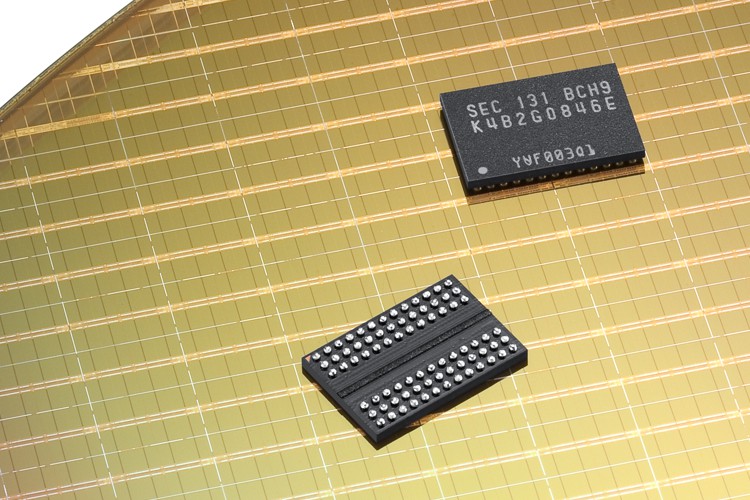

三星的 1z nm 屬於第三代 10nm 級製程,10nm 級製程並不是 10nm,由於 20nm 節點之後 DRAM 的製程升級變得困難,所以 DRAM 記憶體製程的線寬指標不再那麼精確,於是有了 1x nm、 1y nm及 1z nm 之分,簡單來說 1x nm 製程相當於 16-19nm,1y nm 相當於 14-16nm,1z nm 大概是 12-14nm 級別,而在這之後還有 1α 及 1β 製程。

由於先進製程採用 EUV 微影技術已是趨勢,在台積電第二季 EUV 技術 7+nm 進入量產階段並獲華為海思訂單後,三星晶圓代工也採 用EUV 量產 7nm 製程,Intel 預期2021年 7nm 會首度導入 EUV 技術。而隨著製程持續推進至 5nm 或 3nm 後,EUV 光罩層會明顯增加2~3倍以上,對 EUV 光罩盒需求亦會出現倍數成長。

來源:

https://www.dramx.com/News/made-sealing/20190618-16834.html

https://www.expreview.com/68993.html

據悉,三星預期在今年11月開始量產採用 EUV 技術的 1z nm DRAM,量產初期將與三星晶圓代工共享 EUV 設備,初期使用量雖不大,但卻等於宣示 DRAM 光罩微影技術會朝 EUV 方向發展。至於 SK Hynix 及 Micron 也已表明開始評估採用 EUV 技術,業界預期將可能在 1α nm 或 1β nm 世代開始導入。

三星的 1z nm 屬於第三代 10nm 級製程,10nm 級製程並不是 10nm,由於 20nm 節點之後 DRAM 的製程升級變得困難,所以 DRAM 記憶體製程的線寬指標不再那麼精確,於是有了 1x nm、 1y nm及 1z nm 之分,簡單來說 1x nm 製程相當於 16-19nm,1y nm 相當於 14-16nm,1z nm 大概是 12-14nm 級別,而在這之後還有 1α 及 1β 製程。

由於先進製程採用 EUV 微影技術已是趨勢,在台積電第二季 EUV 技術 7+nm 進入量產階段並獲華為海思訂單後,三星晶圓代工也採 用EUV 量產 7nm 製程,Intel 預期2021年 7nm 會首度導入 EUV 技術。而隨著製程持續推進至 5nm 或 3nm 後,EUV 光罩層會明顯增加2~3倍以上,對 EUV 光罩盒需求亦會出現倍數成長。

來源:

https://www.dramx.com/News/made-sealing/20190618-16834.html

https://www.expreview.com/68993.html