上個月在英國舉行的 HPC-AI 會議上,AMD 揭露了一些關於他們未來的 Zen 3 / Zen 4 架構部分訊息,並同時提供了未來的處理器路線圖和有關於下一代代號為 Milan 以及後繼任代號為 Genoa 的 EPYC 處理器的一些關鍵特性。

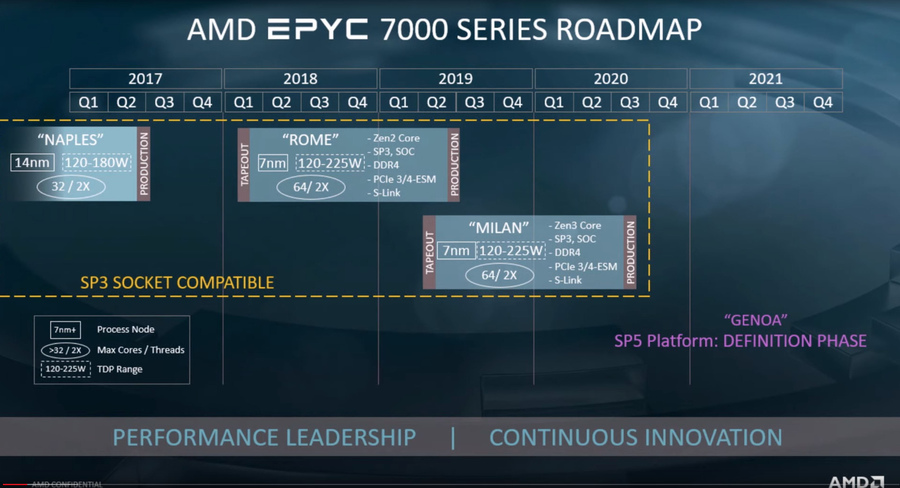

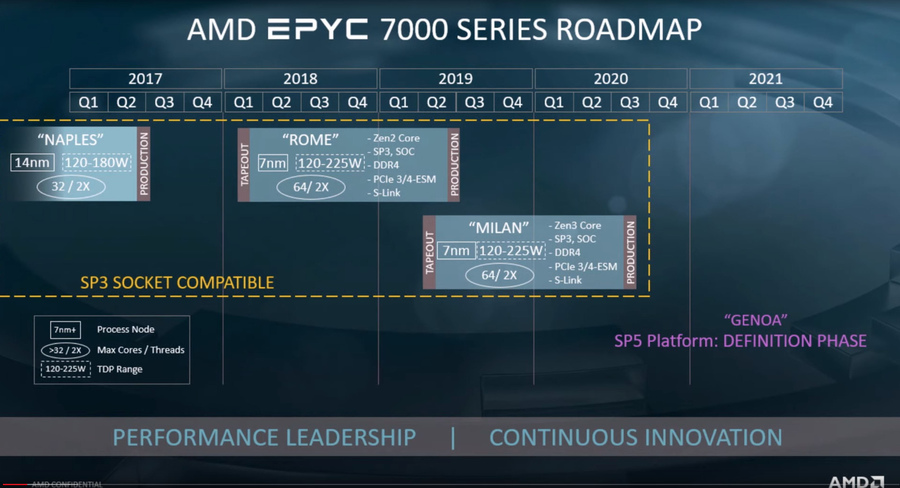

從路線圖上面可以看到,目前代號為 Milan 的第3代 EPYC 處理器已經完成設計並且生產了一些試樣出來,這意味著 AMD 的合作夥伴可能已經拿到了第3代 EPYC 處理器。如果順利的話,AMD 的 Zen 架構將在明年迎來第三代,目前知道的是 AMD 已經完成了對於 Zen 3 架構的設計,並將於2020年第3季度使用台積電的7nm+量產。而從會議上面公佈的關於 Milan 的一些訊息中,我們可以看到 Zen 3 架構的一些差異。

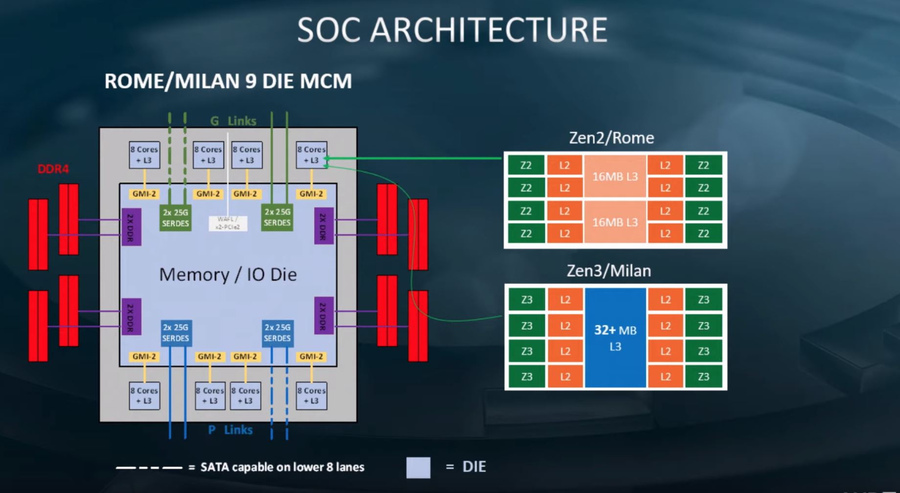

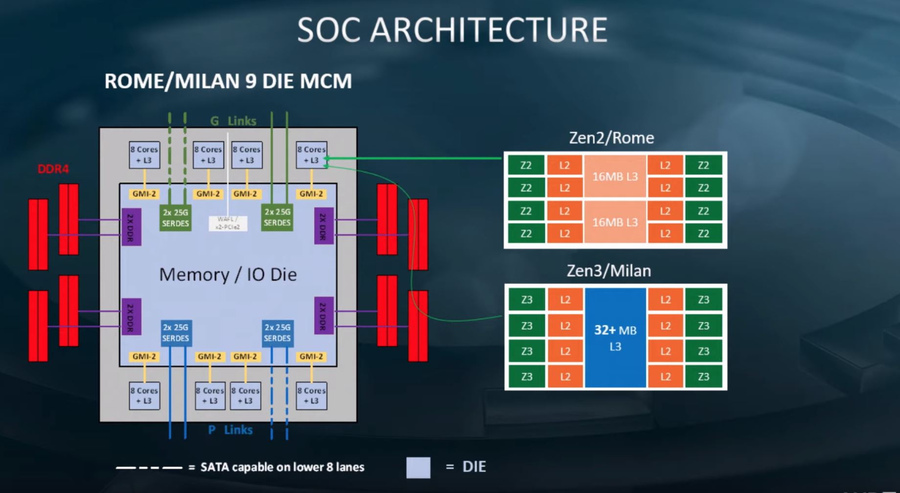

最明顯的是右邊 CCD 的結構差異。原本在 Zen 2 上面,每個 CCD 上含有2個 CCX,一個 CCX 有4個 CPU 核心。而一個 CCD 上面的兩個 CCX 共享同樣的16MB三級快取,所以一塊8核的 Zen 2 CPU 擁有32MB的快取,但它們是由分別位於兩個 CCX 中的16MB三級快取組合而成的。而在 Zen 3 上面,AMD 將原本的分離式三級快取改成了整個 CCD 共享同一塊三級快取。對於現代處理器來說,三級快取是非常重要的,它甚至可以提供一些 IPC 提升,而 CCD 內共享三級快取可以使同一塊 CCD 上面的8個核心間數據交換的延遲減小,尤其是對於跨 CCX 的數據交換來說,這個提升會很明顯。

另外可以看到,Zen 3 架構將仍然使用 MCM 封裝的形式,I/O 核心部分並沒有大改,而從路線圖上面還可以知道,此前傳聞中 AMD 正在研發的單核四線程超線程技術並不會在 Zen 3 上面應用,而可能將會在 Genoa 或更後面的 CPU 上面使用。

而 Milan 和目前的 Roma 系列處理器間將保持良好的向下相容性,將使用同樣的 SP3 插座,在 I/O 支援方面也基本一致。所以目前已知的主要改進點在 CCD 的快取上面,不過關於 CPU 計算架構的細節 AMD 表示目前已經開始研發下一代 Genoa 架構,它將使用新的 Zen 4 架構,搭配新規格的記憶體——可能就是 DDR5,並且可能會直接過渡到 PCIe 5.0。

來源:https://www.expreview.com/70803.html

從路線圖上面可以看到,目前代號為 Milan 的第3代 EPYC 處理器已經完成設計並且生產了一些試樣出來,這意味著 AMD 的合作夥伴可能已經拿到了第3代 EPYC 處理器。如果順利的話,AMD 的 Zen 架構將在明年迎來第三代,目前知道的是 AMD 已經完成了對於 Zen 3 架構的設計,並將於2020年第3季度使用台積電的7nm+量產。而從會議上面公佈的關於 Milan 的一些訊息中,我們可以看到 Zen 3 架構的一些差異。

最明顯的是右邊 CCD 的結構差異。原本在 Zen 2 上面,每個 CCD 上含有2個 CCX,一個 CCX 有4個 CPU 核心。而一個 CCD 上面的兩個 CCX 共享同樣的16MB三級快取,所以一塊8核的 Zen 2 CPU 擁有32MB的快取,但它們是由分別位於兩個 CCX 中的16MB三級快取組合而成的。而在 Zen 3 上面,AMD 將原本的分離式三級快取改成了整個 CCD 共享同一塊三級快取。對於現代處理器來說,三級快取是非常重要的,它甚至可以提供一些 IPC 提升,而 CCD 內共享三級快取可以使同一塊 CCD 上面的8個核心間數據交換的延遲減小,尤其是對於跨 CCX 的數據交換來說,這個提升會很明顯。

另外可以看到,Zen 3 架構將仍然使用 MCM 封裝的形式,I/O 核心部分並沒有大改,而從路線圖上面還可以知道,此前傳聞中 AMD 正在研發的單核四線程超線程技術並不會在 Zen 3 上面應用,而可能將會在 Genoa 或更後面的 CPU 上面使用。

而 Milan 和目前的 Roma 系列處理器間將保持良好的向下相容性,將使用同樣的 SP3 插座,在 I/O 支援方面也基本一致。所以目前已知的主要改進點在 CCD 的快取上面,不過關於 CPU 計算架構的細節 AMD 表示目前已經開始研發下一代 Genoa 架構,它將使用新的 Zen 4 架構,搭配新規格的記憶體——可能就是 DDR5,並且可能會直接過渡到 PCIe 5.0。

來源:https://www.expreview.com/70803.html