隨著半導體製程的升級難度越來越大,進度越來越緩慢,台積電的7nm製程開發成本已經超過了30億美元,接下來的5nm製程預計要超過50億美元,在平面上想提升晶體管密度這事情已經變得相當有挑戰性,3D堆疊製程可能是解決這問題的一個好方法,結構簡單的 NAND 已經大面積轉向3D堆疊製程了,HBM 記憶體也是利用3D堆疊製程生產的,但是3D堆疊製程也不是萬能的,散熱就是3D堆疊製程要面臨的一大難題,層數越多熱量堆積就越嚴重,AMD 近日申請的一項專利就有可能解決這一問題的。

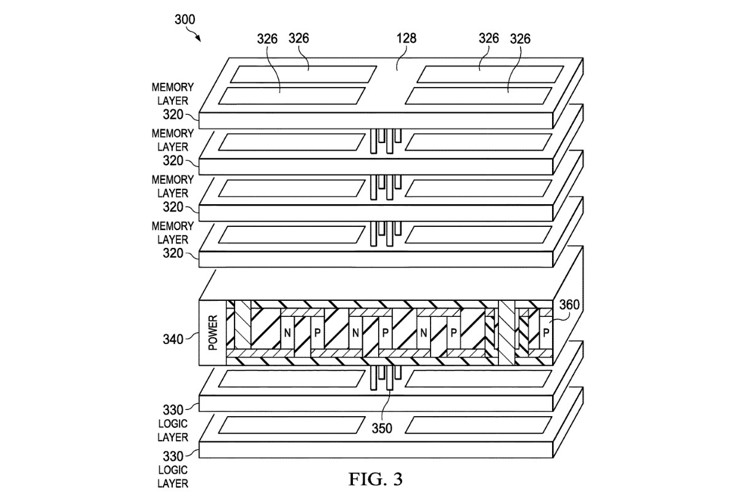

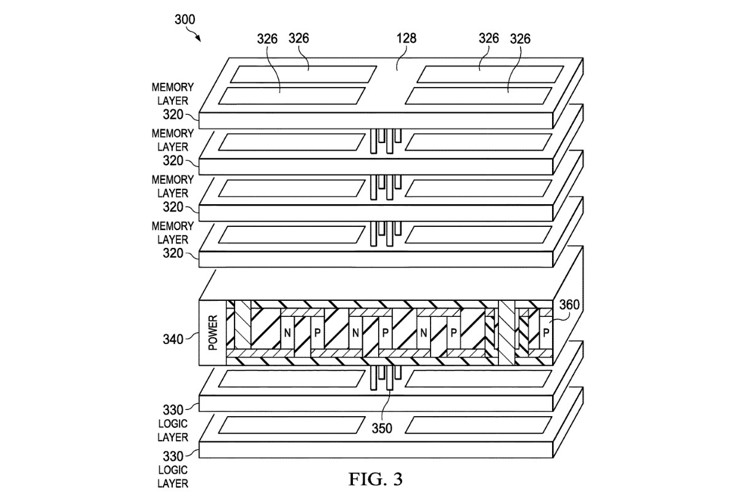

AMD 這一專利的就是在3D堆疊的邏輯層和儲存層之間插入一片 TEC 熱點效應散熱模組,也就是半導體製冷器或溫差製冷器,它利用帕爾貼效應,由N 、P型材料組成一對熱電偶,當熱電偶通入直流電流後,因直流電通入的方向不同,將在電偶結點處產生吸熱和放熱現象。

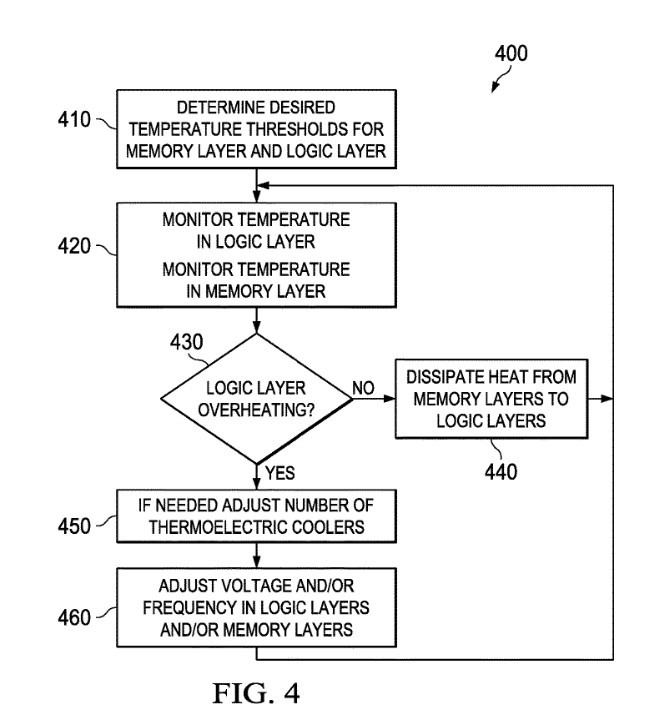

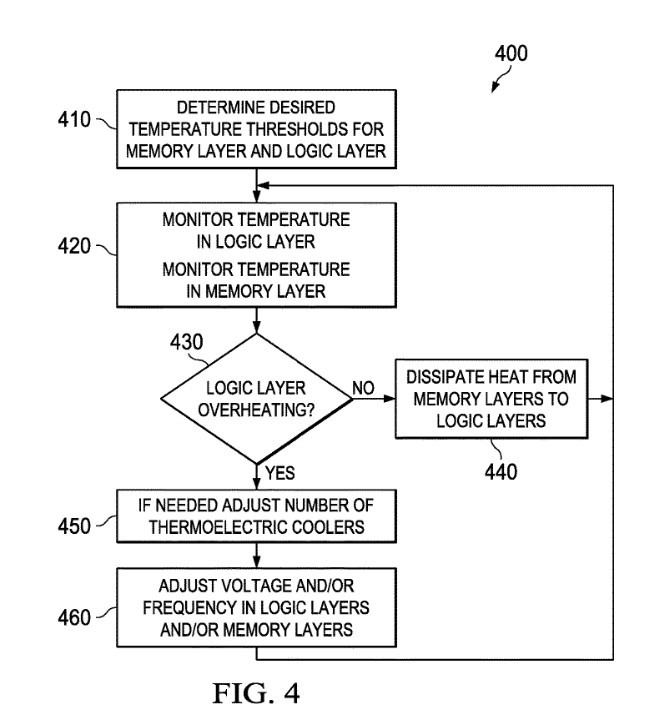

而這個現像是可以根據電流的方向而反轉的,也就是說可以根據傳感器反饋的結果,都可以利用熱電偶把熱量從較高的那一端轉移到溫度較低的一端,讓熱量分佈更為平均,這一專利在任何 3D 堆疊生產的晶片上都相當實用,然而這一過程是會產生額外的發熱的,也會帶來額外的功耗,所以這一專利是否真的有用還得等實際產品出來再說。

來源:https://www.expreview.com/69182.html

AMD 這一專利的就是在3D堆疊的邏輯層和儲存層之間插入一片 TEC 熱點效應散熱模組,也就是半導體製冷器或溫差製冷器,它利用帕爾貼效應,由N 、P型材料組成一對熱電偶,當熱電偶通入直流電流後,因直流電通入的方向不同,將在電偶結點處產生吸熱和放熱現象。

而這個現像是可以根據電流的方向而反轉的,也就是說可以根據傳感器反饋的結果,都可以利用熱電偶把熱量從較高的那一端轉移到溫度較低的一端,讓熱量分佈更為平均,這一專利在任何 3D 堆疊生產的晶片上都相當實用,然而這一過程是會產生額外的發熱的,也會帶來額外的功耗,所以這一專利是否真的有用還得等實際產品出來再說。

來源:https://www.expreview.com/69182.html