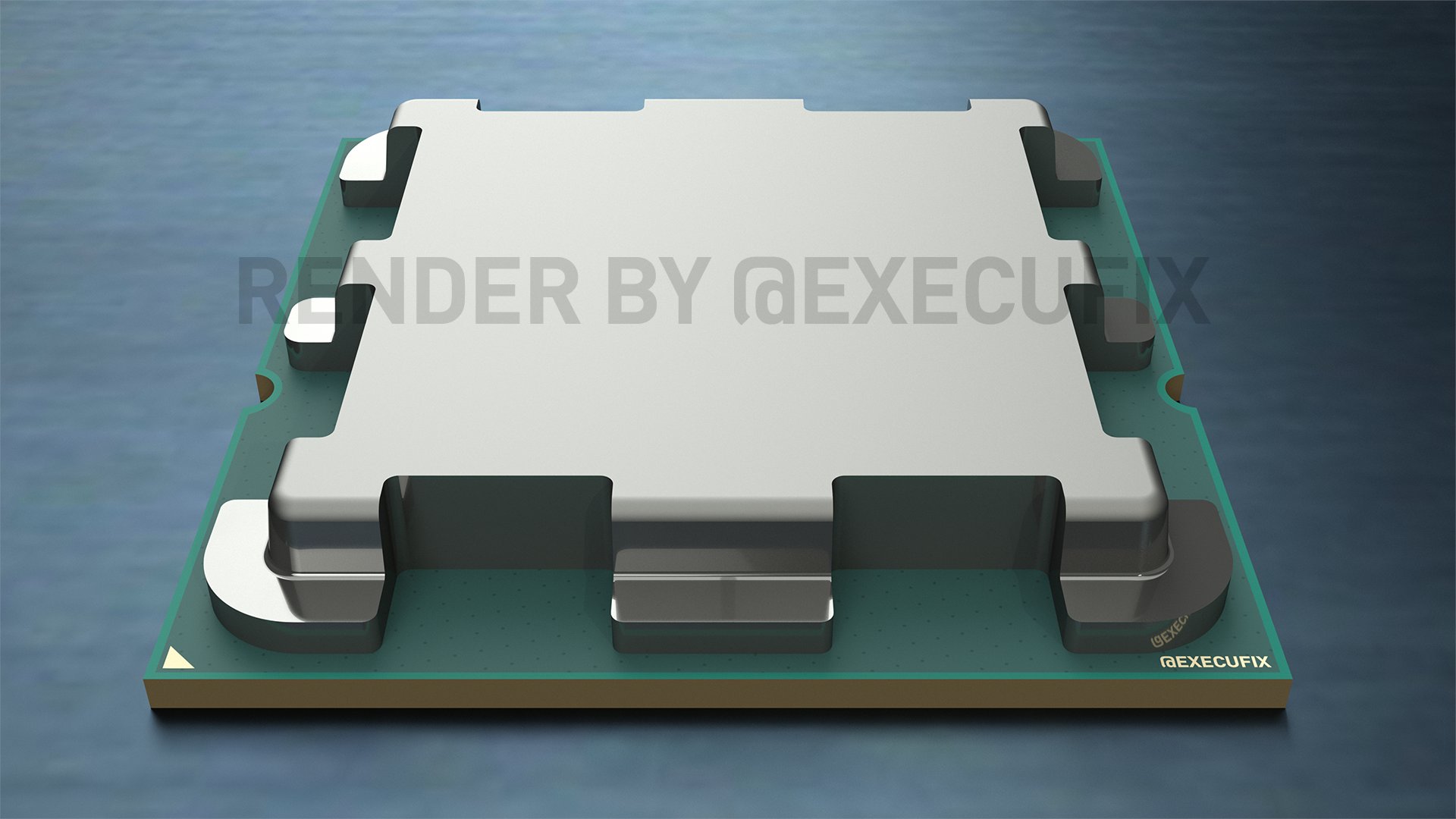

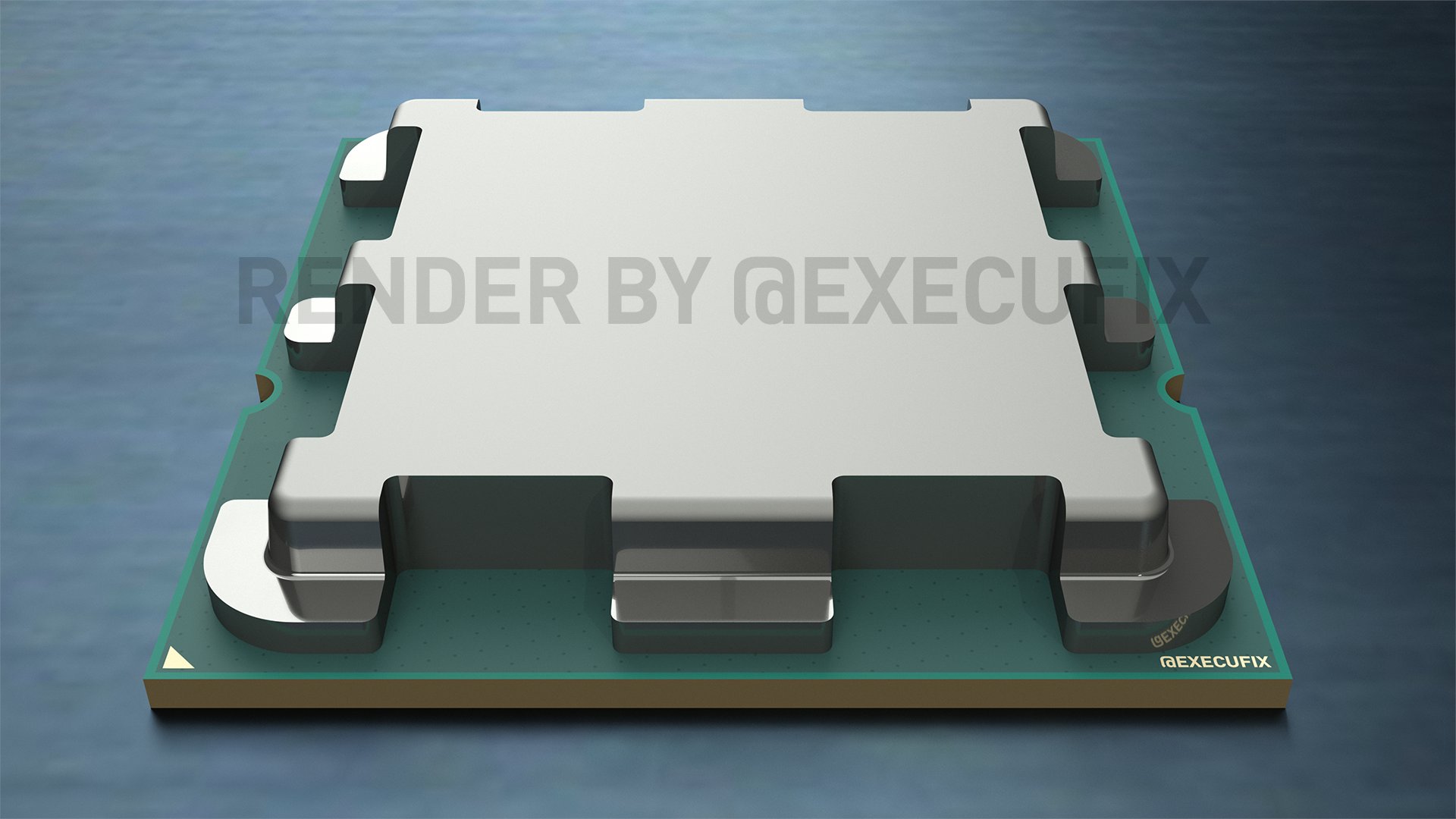

Intel 將在11月4日販售第12代處理器,而 AMD 則會在明年初更新配備 3D V-Cache 技術的 Zen 3 架構桌面處理器,同時在2022年末發布新一代 Zen 4 架構處理器,以應對 Intel 應該會更新的第13代處理器。

之前因某廠被駭客攻擊進而大量機密文件被竊取,裡面曝光了一些 Zen 4 架構細節,如無意外,Zen 4 架構的 L1 指令 / 資料快取依舊是 32KB、關聯8路,但 L2 快取將相比 Zen 3 架構翻倍,從 512KB 變成 1MB,不過仍關聯8路,L3 快取並未列出,可能設計尚未決定。在 Intel Alder Lake 的大小核 Golden Cove 架構和 Gracemont 架構核心,L2 快取對應是每核心 1.25MB 和每四個核心 2MB,這意味著 Alder Lake 完整配置的 L2 快取總共有14MB。Zen 4 架構在配備16個核心的情況下,L2 會有16MB,這將大於 Alder Lake。

雖然 Intel 和 AMD 在快取設計上有所區別,容量大小只是其中一方面,還有其他技術的運用,特別是 Alder Lake 這種混合架構會有較大差異,但不能否認 L1 和 L2 快取在分支預測中發揮著重要的作用。Zen 3 架構通過採用 3D 堆疊技術,為每個 CCX 帶來額外的 64MB 7nm SRAM 快取,使得處理器整體遊戲效能提高15%(AMD 官方說法),提升幅度如同架構的改進。在現代處理器裡,快取體系在 IPC 中扮演了重要的角色,也是評估架構的關鍵之一。

來源

之前因某廠被駭客攻擊進而大量機密文件被竊取,裡面曝光了一些 Zen 4 架構細節,如無意外,Zen 4 架構的 L1 指令 / 資料快取依舊是 32KB、關聯8路,但 L2 快取將相比 Zen 3 架構翻倍,從 512KB 變成 1MB,不過仍關聯8路,L3 快取並未列出,可能設計尚未決定。在 Intel Alder Lake 的大小核 Golden Cove 架構和 Gracemont 架構核心,L2 快取對應是每核心 1.25MB 和每四個核心 2MB,這意味著 Alder Lake 完整配置的 L2 快取總共有14MB。Zen 4 架構在配備16個核心的情況下,L2 會有16MB,這將大於 Alder Lake。

雖然 Intel 和 AMD 在快取設計上有所區別,容量大小只是其中一方面,還有其他技術的運用,特別是 Alder Lake 這種混合架構會有較大差異,但不能否認 L1 和 L2 快取在分支預測中發揮著重要的作用。Zen 3 架構通過採用 3D 堆疊技術,為每個 CCX 帶來額外的 64MB 7nm SRAM 快取,使得處理器整體遊戲效能提高15%(AMD 官方說法),提升幅度如同架構的改進。在現代處理器裡,快取體系在 IPC 中扮演了重要的角色,也是評估架構的關鍵之一。

來源